## Universidad Autónoma de Madrid

Departamento de Ingeniería Informática

## Estimación Estadística de Consumo en FPGAs

# **TESIS DOCTORAL**

Autor: Elías Todorovich

Director: Eduardo Boemo Scalvinoni

Escuela Politécnica Superior

Julio de 2006

## Resumen

Varios motivos impulsan a la industria y a las universidades a estudiar el consumo de energía de los circuitos digitales actuales: movilidad de los equipos electrónicos, coste de los accesorios de refrigeración y encapsulados, impacto medioambiental, coste de la energía, tasa de fallos, y restricciones a la densidad de integración VLSI.

Diseñar circuitos VLSI para bajo consumo requiere de una metodología en cada etapa del proceso de desarrollo. Los principales componentes de tal metodología son estimación y optimización de consumo. A pesar de las muchas técnicas para estimación de consumo publicadas recientemente en la literatura especializada, el problema todavía no está resuelto completamente, ni siquiera al nivel de puertas lógicas. Debido a la complejidad computacional que requiere la estimación de consumo, no puede obtenerse precisión y velocidad al mismo tiempo. Este problema se observa en la estimación de consumo medio para nodos individuales; y para el consumo promedio total en los circuitos secuenciales grandes.

Esta tesis tiene como objetivo estimar el consumo de potencia media a nivel de nodos individuales en FPGAs. Para ello, se desarrolló una plataforma de estimación de consumo con herramientas y estructuras de datos comunes y reusables dentro de una familia de aplicaciones EDA de diseño para bajo consumo. El software desarrollado se integra con las herramientas de Xilinx. Adicionalmente, se ha incorporado el simulador Modelsim dentro del bucle que implementa la técnica propuesta. Igualmente, al haberse usado formatos estándares para el intercambio de datos, es posible integrar la herramienta desarrollada en esta tesis en ambientes de diseño para FPGA de otros fabricantes, y lo mismo para otros simuladores que soporten formatos estándares.

Para validar los resultados, se realizaron más de 1500 simulaciones y experimentos sobre dispositivos Virtex, Virtex-E y Virtex-II cubriendo 10 años de evolución de la tecnología de dispositivos lógicos programables. Las medidas físicas obtenidas permitieron orientar la investigación y a la vez facilitar la evaluación, calibración y depuración del software. El resultado es una herramienta precisa de estimación

desarrollada sobre una plataforma general para el diseño de circuitos de bajo consumo.

## **Abstract**

There are several reasons that strongly lead the industry and the researchers to study the power consumption of the current digital circuits: mobile electronic devices, refrigeration accessories and packaging costs, environmental impact, energy cost, reliability, and restrictions to the VLSI integration density.

Designing VLSI for low power requires a design methodology at every level of the design process. The main components of such a methodology are estimation and optimization. Despite the several techniques recently proposed for power estimation, the problem is not completely solved yet, even at the gate level. Due to the computing complexity of power estimation, accuracy and speed can not be met together. This problem is observed for individual gate average power, and for total average power estimation in large sequential circuits.

The goal in this thesis is the average power estimation at the individual nodes level on FPGAs. In order to do it, a power estimation framework was developed. This general framework has common tools and data structures that can be reused within a family of EDA tools for low power design. At this time this software is integrated with that provided by Xilinx, and its operation has been evaluated with the Modelsim simulator. However, due to the use of standard formats, an easy integration is expected in other design environments for FPGA, and the same feature for simulators that support standard formats.

More than 1500 simulation runs and experiments were performed with Virtex, Virtex-E and Virtex-II devices on available development boards covering 10 years of PLD evolution. These physical measurements allowed the evaluation, tuning and debugging of the developed software. As a result an accurate tool was developed over the mentioned power estimation framework.

# **Agradecimientos**

A Eduardo Boemo, director y amigo, fundamentalmente por haberme dado una oportunidad; por hacer posible este trabajo no sólo en el plano académico, sino también en otros aspectos más mundanos pero vitales en la supervivencia del doctorando, y por tantísimas actitudes como invitarnos los domingos a su casa estando recién llegados a España: gracias. Maite: muchas gracias.

Esta tesis tampoco sería posible sin la confianza de Javier Garrido y Francisco Gómez Arribas, la solidaridad más allá del compañerismo de Sergio López Buedo, la amistad de los compañeros del laboratorio: Gustavo Sutter, Iván González, Juan González Gómez, Guillermo González, Estanislao Aguayo, Alberto Regadío, Alberto Martín-Ortega Rico, y muchos otros becarios y profesores, que durante estos años pusieron la mejor predisposición para el desarrollo de los trabajos en un ambiente de camaradería. Gracias también a Martín Gilabert por su trabajo y entusiasmo en las primeras experiencias vinculadas con esta tesis. Mi reconocimiento especial es para el Prof. Javier Martínez.

Sin Juana Calle no sólo me hubiera sido mucho más difícil cumplir con todo el formalismo que se requiere en un doctorado, sino que no habría mantenido el ritmo académico que hace que estos estudios tengan un final a su debido tiempo. Muchas gracias Juana por tus e-mails y por toda tu ayuda, y tu responsabilidad y seriedad dentro del afecto que pones en tu trabajo. Gracias también a Pablo y a todo el personal de la EPS. Espero ser capaz de mostrarles a todos mi gratitud.

También debo agradecer a las siguientes instituciones argentinas y españolas por su apoyo en esta investigación, por orden de aparición en el desarrollo de las tareas:

- Facultad de Ciencias Exactas de la Universidad Nacional del Centro de la Provincia de Buenos Aires

- CONICET (Consejo Nacional de Investigaciones Científicas y Técnicas) de la República Argentina

- Ministerio de Ciencia y Tecnología de España

- Escuela Politécnica Superior de la Universidad Autónoma de Madrid

Escuela Politécnica Superior de Gandía, de la Universidad Politécnica de Valencia

En lo que concierne a la revisión del texto en inglés, le agradezco especialmente a Walter Routley, y también a Gery Bioul, Hernán Techeiro y naturalmente a Eduardo por su trabajo y paciencia.

Es bueno hacer memoria y este balance al final de un trabajo tan largo. Le doy las gracias de todo corazón a mi familia, amigos y a Dios.

# **Table of Contents**

| <u>1 II</u>       | NTRODUCTION                      | 1  |

|-------------------|----------------------------------|----|

|                   |                                  |    |

| 1.1               | AVERAGE POWER CONSUMPTION        | 2  |

| 1.1.1             | PORTABLE ELECTRONIC PRODUCTS     | 2  |

| 1.1.2             | ENVIRONMENTAL IMPACT             | 3  |

| 1.2               | MAXIMUM POWER CONSUMPTION        | 4  |

| 1.3               | POWER CONSUMPTION IN FPGAS       | 6  |

| 1.4               | RESEARCH OBJECTIVES              | 7  |

| 1.5               | THESIS ORGANIZATION              | 8  |

| REFE              | ERENCES                          | 9  |

| <u>2</u> <u>V</u> | LSI POWER CONSUMPTION            | 11 |

| 2.1               | ANALYSIS OF POWER CONSUMPTION    | 12 |

| 2.1.1             | THERMODYNAMICS OF COMPUTATION    | 12 |

| 2.1.2             | SOURCES OF POWER DISSIPATION     | 14 |

| 2.2               | POWER CONSUMPTION IN FPGAS       | 18 |

| 2.2.1             | PROGRAMMABLE ROUTING             | 19 |

| 2.2.2             | PHYSICAL CAPACITANCE             | 20 |

| 2.2.3             | SWITCHING ACTIVITY               | 21 |

| 2.3               | SWITCHING ACTIVITY COMPUTATION   | 22 |

| 2.3.1             | DEPENDENCE ON THE INPUT PATTERNS | 22 |

| 2.3.2             | DELAY MODEL                      | 25 |

| 2.3.3             | LOGIC FUNCTION                   | 27 |

| 2.3.4             | CIRCUIT STRUCTURE                | 28 |

| 2.3.5             | TECHNOLOGY-DEPENDANT FACTORS     | 29 |

| 2.4               | Conclusions                      | 29 |

| Refe              | ERENCES                          | 30 |

| 3 D               | POWER ESTIMATION TECHNIQUES      | 33 |

| 3.1               | POWER ESTIMATION HISTORY -OR SIMULATIVE APPROACHES  | 35 |

|-------------------|-----------------------------------------------------|----|

| 3.1.1             | SPICE-LIKE CIRCUIT SIMULATION                       | 35 |

| 3.2               | STATISTICAL APPROACHES                              | 37 |

| 3.2.1             | MONTE CARLO SIMULATION                              | 37 |

| 3.2.2             | TOTAL POWER (MCPOWER)                               | 38 |

| 3.2.3             | POWER OF INDIVIDUAL GATES (MED)                     | 40 |

| 3.2.4             | IMPROVEMENTS IN STATISTICAL METHODS                 | 41 |

| 3.3               | PROBABILISTIC APPROACHES                            | 42 |

| 3.3.1             | SOME IMPORTANT DEFINITIONS                          | 43 |

| 3.3.2             | PROBABILISTIC POWER ESTIMATION TECHNIQUES           | 44 |

| 3.4               | SEQUENTIAL CIRCUITS                                 | 48 |

| 3.4.1             | STATISTICAL APPROACHES                              | 48 |

| 3.5               | POWER ESTIMATION METHODS APPLIED ON FPGAS           | 58 |

| 3.5.1             | RELATED WORKS AT THE UAM                            | 60 |

| 3.6               | CONCLUSIONS                                         | 61 |

| REFI              | ERENCES                                             | 61 |

|                   |                                                     |    |

| <u>4</u> <u>A</u> | A-DYP: A TOOL FOR AVERAGE POWER ESTIMATION IN FPGAS | 65 |

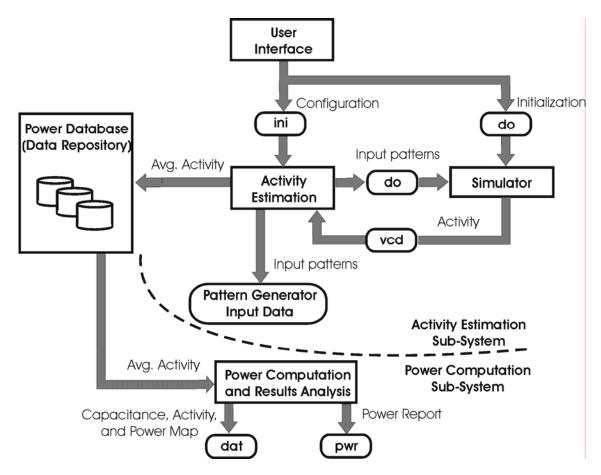

| 4.1               | A-DYP MAIN STRUCTURE                                | 67 |

| 4.2               | THE PREPARATION PHASE                               | 68 |

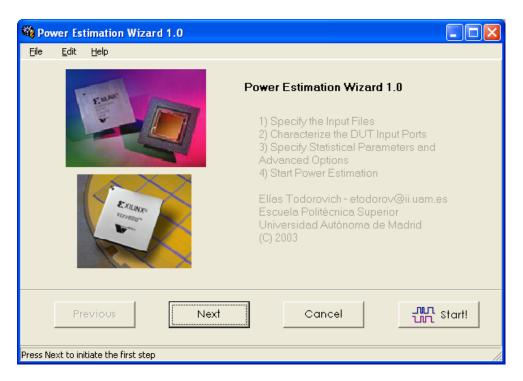

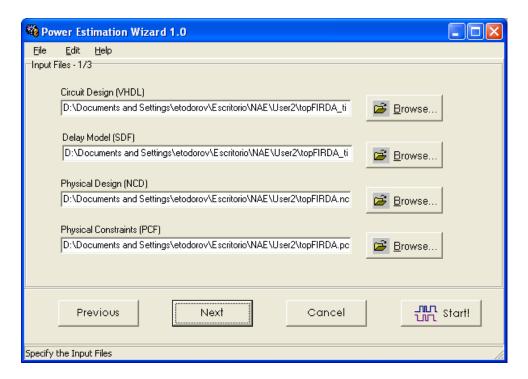

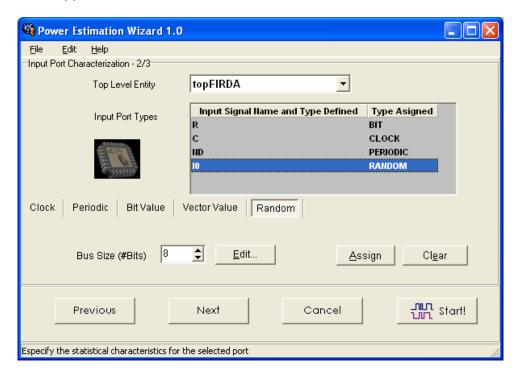

| 4.2.1             | USER INTERFACE                                      | 70 |

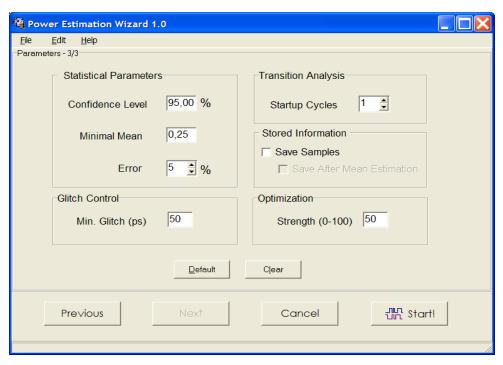

| 4.2.2             | POWER ESTIMATION SET-UP PHASE                       | 73 |

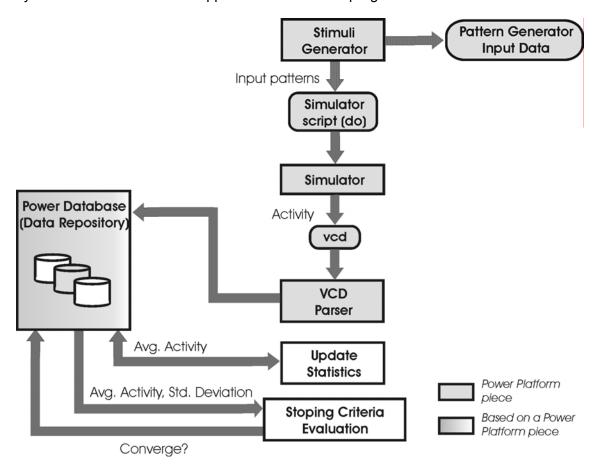

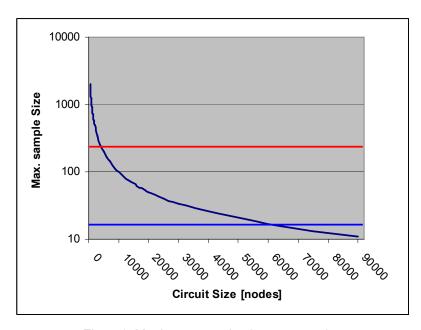

| 4.3               | ACTIVITY ESTIMATION SUB-SYSTEM                      | 74 |

| 4.3.1             | INPUT PATTERNS FOR THE PATTERN GENERATOR            | 77 |

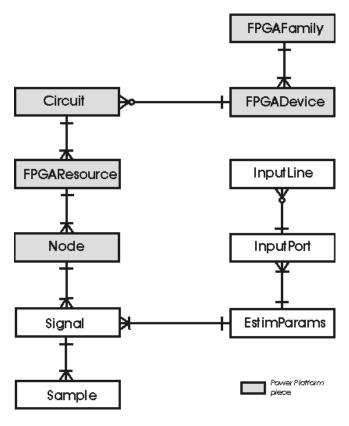

| 4.3.2             | THE POWER ESTIMATION PLATFORM                       | 78 |

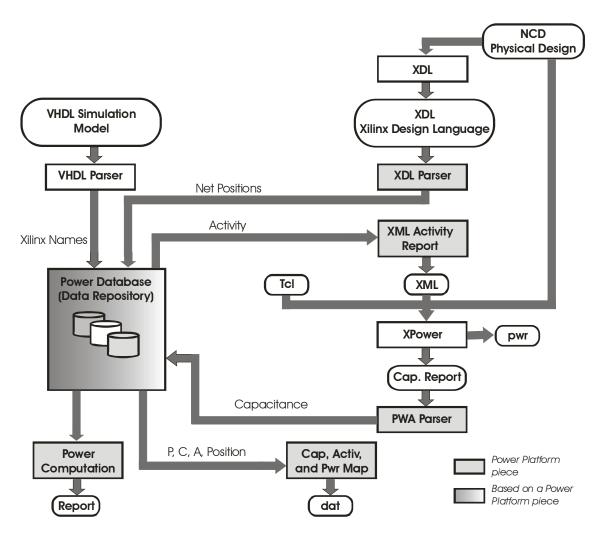

| 4.4               | POWER COMPUTATION SUB-SYSTEM                        | 78 |

| 4.5               | THE POWER DATABASE                                  | 82 |

| 4.6               | Conclusions                                         | 84 |

| REF               | ERENCES                                             | 85 |

| 5 A               | ACTIVITY ESTIMATION SUB-SYSTEM                      | 87 |

| 5.1 THE PATTERN GENERATOR                                           | 88  |

|---------------------------------------------------------------------|-----|

| 5.2 SIMULATING THE INPUT PATTERNS AND SAVING THE SIMULATION RESULTS | 91  |

| 5.3 ANALYZING THE GENERATED ACTIVITY                                | 93  |

| 5.3.1 THE SET-UP PERIOD                                             | 93  |

| 5.3.2 COUNTING THE EFFECTIVE TRANSITION NUMBER                      | 94  |

| 5.4 UPDATING NODE STATISTICS                                        | 95  |

| 5.5 CHECKING THE STOPPING CRITERIA                                  | 97  |

| 5.6 CONCLUSIONS                                                     | 97  |

| REFERENCES                                                          | 97  |

|                                                                     |     |

| 6 POWER COMPUTATION SUB-SYSTEM                                      | 99  |

| 6.1 PARSING THE VHDL SIMULATION MODEL                               | 100 |

| 6.1.1 WHY PARSING THE VHDL MODEL?                                   | 101 |

| 6.1.2 OBTAINING THE IDENTIFIERS                                     | 103 |

| 6.1.3 OPTIMIZATION                                                  | 105 |

| 6.2 PARSING THE XILINX DESIGN XDL FILE                              | 105 |

| 6.2.1 Analyzing an FPGA Slice Definition                            | 106 |

| 6.2.2 Analyzing a Net Definition                                    | 109 |

| 6.3 GENERATING THE XML SETTINGS FILE                                | 111 |

| 6.3.1 USING A PACKAGE TO GENERATE XML                               | 112 |

| 6.4 EXTRACTING THE CAPACITANCES                                     | 113 |

| 6.4.1 PARSING THE XILINX CAPACITANCE REPORT FILE (PWA)              | 114 |

| 6.5 CALCULATING THE POWER CONSUMPTION AND WRITING A REPORT          | 115 |

| 6.6 GENERATING THE POWER MAPS                                       | 116 |

| 6.7 Conclusions                                                     | 116 |

| REFERENCES                                                          | 117 |

|                                                                     |     |

| 7 TEST CASES AND ANALYSIS                                           | 119 |

| 7.1. TEST CIRCUITS                                                  | 119 |

| 7.1.1 QUADRATURE DIRECT DIGITAL FREQUENCY SYNTHESIZERS (QDDFS)      | 119 |

| 7.1.2 DISTRIBUTED-ARITHMETIC FIR FILTER (FIRDA)                     | 122 |

| 7.1.3             | FAST FOURIER TRANSFORM (FFT)                         | 123 |

|-------------------|------------------------------------------------------|-----|

| 7.1.4             | ARITHMETIC CIRCUITS                                  | 123 |

| 7.2               | ANALYSIS OF THE RESULTS                              | 124 |

| 7.2.1             | TECHNIQUE CHARACTERIZATION                           | 124 |

| 7.2.2             | SOFTWARE EVALUATION                                  | 125 |

| 7.2.3             | GRAPHICAL REPRESENTATION OF THE RESULTS              | 126 |

| <b>7.3</b>        | POWER MEASUREMENT                                    | 126 |

| REFE              | RENCES                                               | 129 |

|                   |                                                      |     |

| <u>8</u> <u>E</u> | XPERIMENTAL RESULTS                                  | 131 |

|                   |                                                      |     |

| 8.1               | A-DYP PRELIMINARY EVALUATION                         | 132 |

| 8.1.1             | TOTAL DYNAMIC POWER ESTIMATION                       | 133 |

| 8.1.2             | IMPACT OF THE INPUT PATTERNS DEFINITION              | 134 |

| 8.1.3             | TOOL'S EVALUATION                                    | 135 |

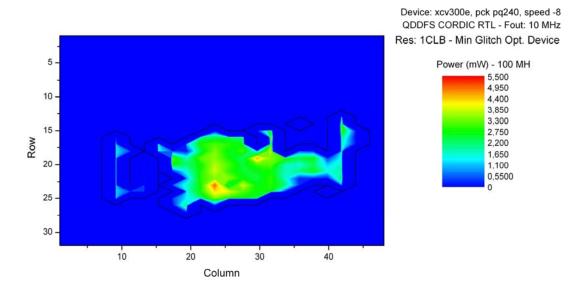

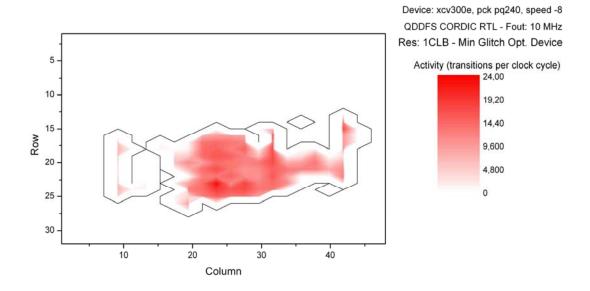

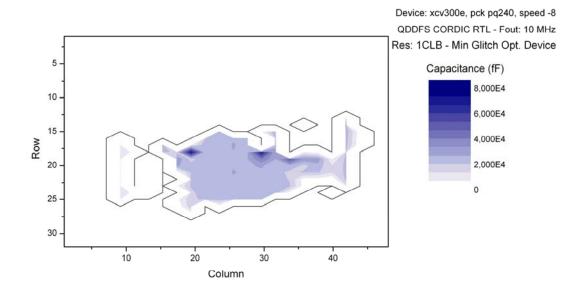

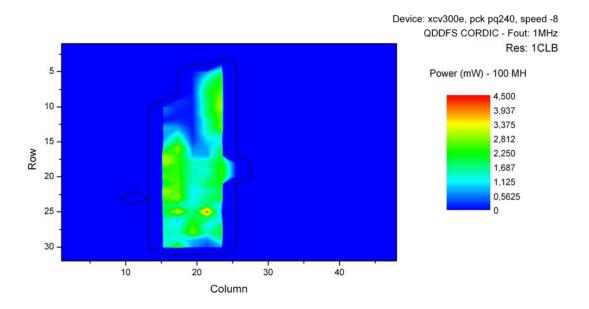

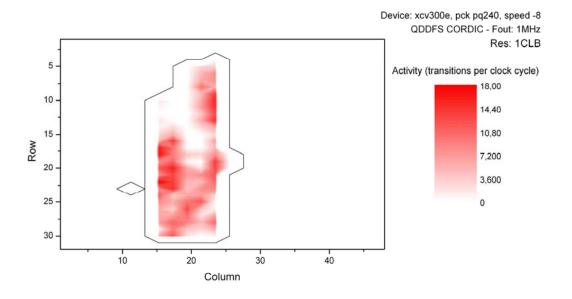

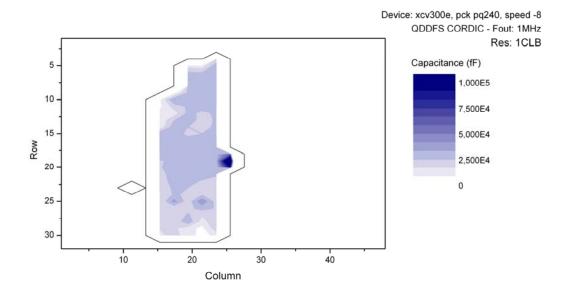

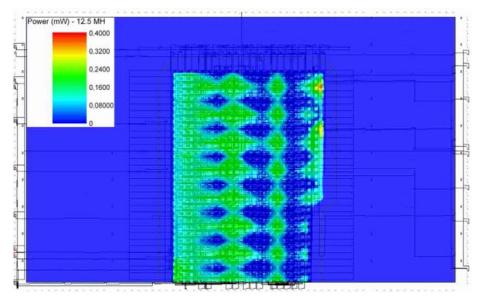

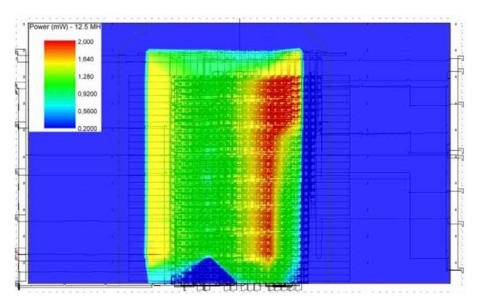

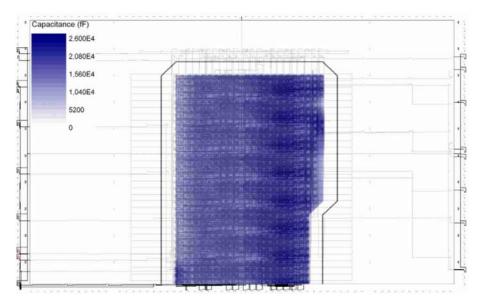

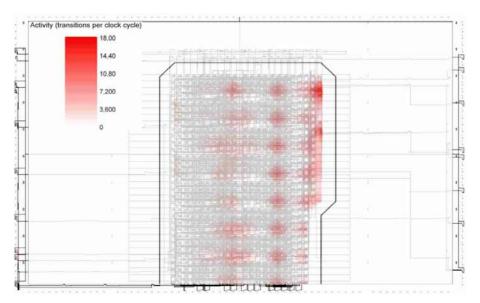

| 8.1.4             | POWER MAPS                                           | 136 |

| 8.2               | A FIRST COMPLETE TEST CASE: FIRDA FILTERS            | 139 |

| 8.2.1             | TOTAL DYNAMIC POWER ESTIMATION                       | 139 |

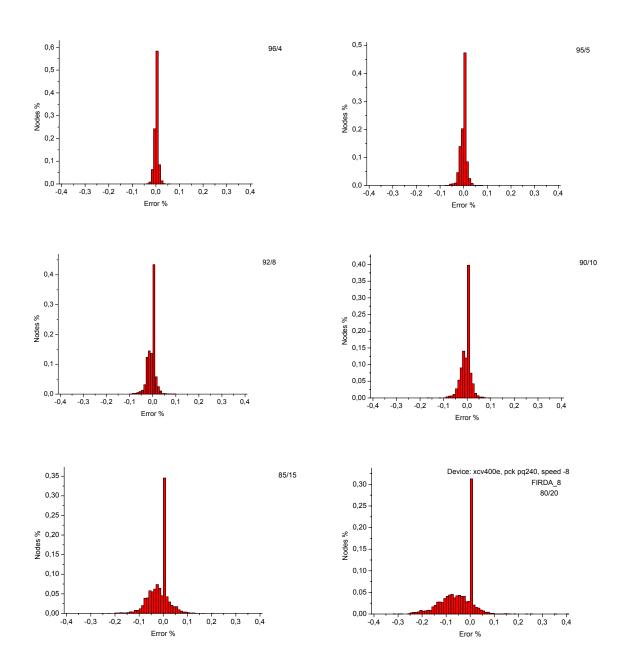

| 8.2.2             | ESTIMATING POWER FOR INDIVIDUAL NODES                | 140 |

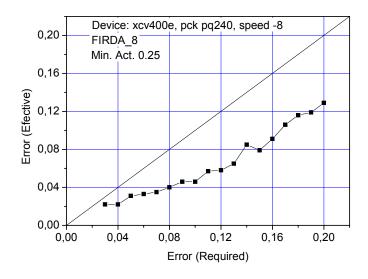

| 8.2.3             | ACCURACY VS. EXECUTION TIME TRADEOFF                 | 147 |

| 8.2.4             | TOOL'S EVALUATION                                    | 152 |

| 8.2.5             | POWER MAPS                                           | 154 |

| 8.2.6             | ENERGY ANALYSIS OR ENERGY OF THE COMPUTATION         | 158 |

| 8.3               | IMPACT OF THE INPUT PATTERNS DEFINITION              | 160 |

| 8.3.1             | TOTAL DYNAMIC POWER ESTIMATION                       | 162 |

| 8.3.2             | DYNAMIC POWER ESTIMATION FOR INDIVIDUAL NODES        | 166 |

| 8.3.3             | INPUT PATTERNS FROM REAL SCENARIOS                   | 168 |

| 8.4               | Additional Experiments on Virtex-II                  | 171 |

| 8.4.1             | IMPACT OF THE INPUT PATTER DEFINITION ON TOTAL POWER | 172 |

| 8.4.2             | DYNAMIC POWER ESTIMATION FOR INDIVIDUAL NODES        | 173 |

| 8.4.3             | ACCURACY VS. EXECUTION TIME TRADEOFF                 | 175 |

| 8.4.4             | TOOL'S EVALUATION                                    | 178 |

| 8.4.5             | POWER MAPS                                           | 179 |

| 8.5 CONCLUSIONS                                       | 181 |

|-------------------------------------------------------|-----|

| REFERENCES                                            | 182 |

| 9 CONCLUSIONS AND FUTURE WORKS                        | 183 |

| 9.1 MAIN CONTRIBUTIONS OF THIS THESIS                 | 183 |

| 9.1.1 THE POWER PLATFORM FRAMEWORK AND A-DYP          | 184 |

| 9.1.2 SHORT-PULSE FILTERING AS A CALIBRATION RESOURCE | 185 |

| 9.1.3 A-B NODES CLASSIFICATION                        | 186 |

| 9.1.4 ENERGY OF THE COMPUTATION                       | 186 |

| 9.2 REVERSE ENGINEERING                               | 186 |

| 9.3 Publications                                      | 187 |

| 9.4 FUTURE TASKS                                      | 189 |

| 9.4.1 HIGH-LEVEL POWER ESTIMATION                     | 191 |

| 9.5 HOW TO ESTIMATE POWER CONSUMPTION                 | 192 |

| 9.6 HOW TO BUILD A POWER ESTIMATOR                    | 193 |

| REFERENCES                                            | 193 |

| COMPLETE REFERENCES LIST                              | 195 |

| TCL/TK SCRIPT FOR THE A-DYP POWER ESTIMATION TOOL     | 201 |

| INPUT PATTERNS FILE (.DO)                             | 213 |

| THE CONFIGURATION .INI FILE                           | 215 |

| POWER REPORT FILE                                     | 210 |

# **Acronyms**

API Application Program Interface

ASIC Application Specific IC

ATP Area Time Power

CAD Computer Aided Design

CLB Configurable Logic Block

CMOS Complementary Metal Oxide Semiconductor

DSP Digital Signal Processing

DUT Design Under Test

EDA Electronic Design Automation

FF Flip-Flop

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

IC Integrated Circuit

IDE Integrated Development Environment

IEEE Institute of Electrical and Electronic Engineers

IEEE 1076 IEEE VHDL standard

IEEE 1364 IEEE Verilog HDL standard

iid Independent and identically distributed

IOB Input/Output Block

ITRS International Technology Roadmap for Semiconductors

LUT Look-Up Table

LSB Less Significant Bit

NC Set Near Closed Set

MSB Most Significant Bit

MPU Microprocessor Unit

OVI Open Verilog International

PAR Place and Route

PCB Printed Circuit Board

PPR Partitioning, Place and Route

P&R Place and Route

RTL Register Transfer Level

QAM Quadrature Amplitude Modulation

QDDFS Quadrature Direct Digital Frequency Synthesizer

QPSK Quadrature Phase Shift Keying

SDF Standard Delay Format

TWG Technical Working Group

UUT Unit Under Test

VITAL VHDL Initiative Towards ASIC Libraries

VHDL VHSIC (Very High-Speed IC) HDL

VI VHDL International

# Chapter 1.

"If performance per watt is to remain constant over the next few years, power costs could easily overtake hardware costs, possibly by a large margin." and "...one could envision bizarre business models in which the power company will provide you with free hardware if you sign a long-term power contract." Luiz André Barroso, a principal engineer at Google [Bar05]

## 1 Introduction

Revising the history of the technology [Rab96], power consumption is a recurring problem in an area like digital circuit design where complexity grows according to Moore's law. When CMOS technology was introduced, it was believed that the power consumption problem was solved for digital circuits. In this technology, the static power consumption is very low and the electric current only flows in the circuit when some computing is done. In that time, the major concerns of the VLSI designers were area and performance, and power consumption was mostly of secondary importance. Nevertheless, the number of transistors per unit of area, and the number of transistors in a single die have reached a limit where the power consumption is a problem. Now power is as important as area and speed. But several other factors have contributed to this trend as is briefly discussed below. This is particularly true for FPGAs, where the power consumption noticeably rises due to the increase in the clock frequency, chip area (capacitance), and the ability to be programmed.

Perhaps the primary driving factor that made power consumption as important as area and speed has been the remarkable success and growth of portable electronic products. In these applications, average power consumption is a critical design

concern. In addition, maximum power consumption is also a constraint in the contemporary electronic industry.

In this Chapter, a motivation for low power design is presented together with the research objectives of this thesis,

## 1.1 Average Power Consumption

#### 1.1.1 Portable Electronic Products

MP3 players, pagers, mobile phones, portable CD players, notebooks, etc., demand high-speed computation and complex functionality with low power consumption. In these applications average power consumption is a critical design concern.

Example 1.1: A portable multimedia terminal, when implemented using off-the-shelf components not optimized for low-power operation, consumes about 40 W. For 10 hours of operation between recharges, with a Lithium-Ion battery with 100 Wh/kg of energy density<sup>1</sup>, it will require 4 kg of batteries. Energy density and weight is displayed at Table 1.1 for several battery technologies, including the Lithium-Polymer-Potential technology not yet available in the market.

| Technology                | Energy Density<br>[Wh/kg] | Weight<br>[Kg] |  |

|---------------------------|---------------------------|----------------|--|

| Nickel-Metal-Hydride      | 80                        | 5.00           |  |

| Lithium-lon               | 100                       | 4.00           |  |

| Lithium-Polymer-Potential | 400                       | 1.00           |  |

Table 1.1: Battery Sizing

Example 1.2: A more realistic example can be outlined looking at an actual portable computer running a multimedia application. It consumes 24.8 Watts [Kol01]. In the scenario as in example 1.1 (10 hours of operation between recharges, lithium-ion

$<sup>^{\</sup>rm 1}$  Energy density is the amount of energy stored per unit of weight expressed in watt-hour per kilogram.

battery) this computer will require 2.48 kilograms of battery. Battery sizing for other technologies is shown in Table 1.2.

| Technology                | Energy Density<br>Wh/kg | <b>Weight</b><br>Kg |  |

|---------------------------|-------------------------|---------------------|--|

| Nickel-Metal-Hydride      | 80                      | 3.10                |  |

| Lithium-lon               | 100                     | 2.48                |  |

| Lithium-Polymer-Potential | 400                     | 0.62                |  |

Table 1.2: Battery Sizing

From the examples, we can see that without low-power design techniques portable devices will suffer usability problems.

#### 1.1.2 Environmental Impact

For consumer electronics power savings means significant money saving. It could also be viewed as a long term objective for low power design. The smaller the power dissipation of electronic systems, the lower the heat pumped into the rooms, the lower the electricity consumed and hence the lower the impact on global environment, and less the office noise (e.g., due to elimination of a fan from the desktop), and less the office heat removal requirements [Ped97].

The United States Environmental Protection Agency (EPA) publishes Energy Star guidelines that suggest ways to reduce power consumption and to save money by eliminating unnecessary energy use. Office equipment, led by computers, is the fastest growing electrical load in the business world. In fact, office equipment accounts for 7-20% of all commercial sector electricity usage [Kaw01] [Lai01].

Some works studied the electric energy used by computing equipment ([Ang01] [Kaw00] [Hay01]). [Kaw01] and [Lai01] report that total power use by office and network equipment in the U.S. is about 2% of total electricity use. They also say that power management currently saves 23 % of the energy consumption; and complete saturation with proper power management and night shut down will save 38 %. On a monthly or annual basis, owners could save millions of dollars in electricity costs and the pollution associated with electricity use can be reduced.

## 1.2 Maximum Power Consumption

Table 1.3 shows maximum power consumption trends for MPUs and high performance ASICs according to the ITRS forecast [ITRS05]. These trends are presented in three categories:

- 1) high-performance desktop applications, for which a heat sink on the package is permitted;

- 2) cost-performance, where economical power management solutions of the highest performance are most important; and

- 3) portable battery operations (now designated as the "Harsh" application category by the Assembly and Packaging TWG).

Total power consumption continues to increase, despite the use of a lower supply voltage. The increased power consumption is driven by higher chip operating frequencies; the higher interconnect overall capacitance and resistance, the increasing gate leakage of exponentially growing, and scaled on-chip transistors.

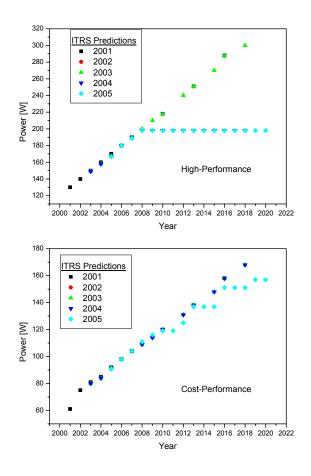

Fig. 1.1 shows maximum power predictions for high-performance and cost performance MPUs and high performance ASICs according to different ITRS updates since 2001. Note that, for high-performance MPU, power consumption significantly exceeds the high-performance single-chip package power limits, even with allowed power densities in excess of 250 W/cm² [ITRS05]. Thus, power will be limited more by system level cooling and test constraints than packaging. This fact is considered from the 2003 forecast.

[Gun01] reports that power consumption of processors produced by Intel almost doubles every 4 years<sup>2</sup>. The cost associated with packaging and cooling of such devices could reach relatively high values.

<sup>&</sup>lt;sup>2</sup> In this moment, there is a controversy about the maximum power dissipation reported by the industry. An independent analyst, [Smi01], reports 72 W of maximum power consumption for the 1.4 GHz Athlon; and 87-88 W for the 1.8 GHz Pentium 4. The same article refer to an interesting concept: the programs used by the vendors to run that tests are safeguarded as restricted information in order to prevent the development of thermal viruses.

|                                    | 2007 | 2010 | 2012 | 2014 | 2016 | 2018 | 2020 |

|------------------------------------|------|------|------|------|------|------|------|

| High-performance with heatsink (W) | 189  | 198  | 198  | 198  | 189  | 198  | 198  |

| Cost-performance (W)               | 104  | 119  | 125  | 137  | 151  | 151  | 157  |

| Battery (W) – (low cost/hand Held) | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  |

Table 1.3: Allowable maximum power for the next years

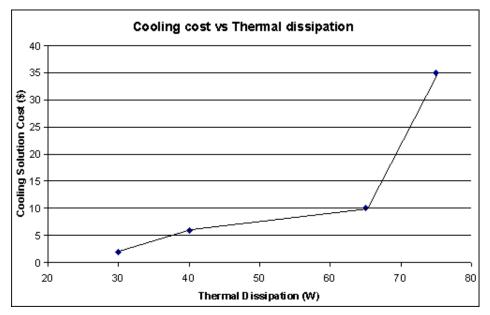

Since core power consumption must be dissipated through the packaging, increasingly expensive packaging, cooling strategies and protection mechanisms are required as chip power consumption increases. Consequently, there is a clear financial advantage to reducing the power consumed in high performance systems (See Fig. 1.2).

Fig. 1.1: Trends in maximum power consumption according to ITRS

Fig 1.2 shows that, as power increases, the relationship between the dissipated power and the cooling solution cost that should be adopted is non-linear.

Fig. 1.2: Cost Associated with Packaging and Cooling Systems. Reproduced from [Gun01]

Reliability is another technological issue. The systems must be designed to ensure that the chip does not exceed the maximum specified operation temperature, even when it is dissipating the maximum power. High power systems often run hot and high temperature trends to increase occurrences of silicon failure mechanisms [Lal97]. For example it has been shown that the switching activity is a valuable parameter to estimate the available working time before failure [Iye86].

Another crucial driving factor is that excessive power consumption is becoming the limiting scale factor in integrating more transistors on a single chip or on a multiple-chip module.

Power supply rail design is a specific topic directly related to the maximum dissipated power.

## 1.3 Power Consumption in FPGAs

Although the background, techniques, research literature, theory, and motivations presented in this thesis are mostly aimed at CMOS circuits, the implemented software is integrated with the Xilinx design flow and experiments are performed on SRAM-

Introduction Research Objectives

based FPGAs of the same vendor. The ability of these programmable logical devices for prototyping, digital electronics teaching and training, adaptation to modern systems with evolving specifications, economical viability for specific markets like industrial automation, control, aerospace, or high-end medical imaging, and the availability of state-of-the-art digital technology for end users all around the world, have spread FPGAs quickly since their commercial launch in 1985 [Wil99]. Furthermore, FPGAs are low cost devices in these contexts and vendors offer friendly development software, tutorials, teaching resources, and tools that enable accessing the technology in a few weeks with a reasonable level of expertise after a relatively short training period. Beyond these applications, FPGAs are also competing with ASICs and DSPs in the digital consumer market.

The specific nature of FPGAs leads to particular design techniques and the EDA tools for them also require specific considerations from their conception (i.e. analysis) to their implementation. The abundant routing resources and programmability significantly affect the device's power consumption. Furthermore, state-of-the-art VLSI technologies are applied to current FPGA production, e.g. 90 nm to Virtex-4 [XDS06] and Altera Stratix-II [Alt05]. This leads to unprecedented integration levels and transistor counts on a single chip which converts FPGA to high-performance ICs with the power consumption problems reported by ITRS [ITRS05]. In this way, it is interesting to evaluate techniques proposed to ASICs and adapt or develop new ones according to FPGA technologies.

## 1.4 Research Objectives

In this work, FPGAs are more than a technological framework in order to verify theoretical research; they are the core of this study. The main goal in this thesis is the average power estimation at the individual nodes level on FPGAs. In order to do it, a power estimation framework is developed. This general framework has common tools and data structures that can be reused within a family of EDA tools for low power design.

The instance of this framework presented in the following chapters is a gate-level statistics-based power estimation tool for both the total and individual nodes power. This tool must produce accurate estimation values, i.e. with less than 10% of error in

the total power in relation to physical measurements over real devices, in a reasonable run time when the required accuracy is moderate, e.g. with 90% confidence that error is less than 10%.

## 1.5 Thesis Organization

This thesis is organized in nine chapters. This chapter has presented a motivation for and introduction to the low-power design problems that will be presented in the next chapters.

Chapter 2 analyzes CMOS and FPGA power consumption and presents the problems that must be overcome in order to estimate power or energy dissipation in these technologies. There is also an interesting summary about thermodynamics of computation in this chapter.

Chapter 3 describes the state-of-the-art in gate-level power estimation with focus on the statistical techniques. These first three chapters make up the introductory part of the thesis.

The lack of modern power estimation tools for FPGAs within commercial design flows, leads us to propose a power estimation framework in Chapter 4 that can support the statistical tool whose activity estimation and power computation parts are detailed in Chapters 5 and 6 respectively.

Chapter 7 presents test circuits used in the power estimation experiments and tool evaluation. This chapter also describes the measurement methodology necessary to generate values against which the estimations are compared. In this way the developed tool can be calibrated and debugged. The development boards and devices employed in the measurements are also briefly presented.

Chapter 8 shows the experimental results in a chronological order where the circuits, devices and tests are joined together in order to evaluate the development and produce a robust EDA tool.

Finally, Chapter 9 presents the main conclusions and topics for future research in the power-aware EDA tools and low-power design areas.

Introduction References

#### References

[Alt05] Altera Corp., "Stratix-II Device Handbook, 2005", available at http://www.altera.com

- [Ang01] J. Angel, "Emerging Technology: Energy Consumption and the New Economy", Network Magazine, January 5, 2001.

- [Bar05] Luiz André Barroso, "The Price of performance", ACM Queue, pp. 49-53, September 2005.

- [Gun01] S.H. Gunther, F. Binns, D.M. Carmean and J.C. Hall, "Managing the Impact of Increasing Microprocessor Power Consumption", Intel Technology Journal Q1, 2001.

- [Hay01] Brian Hayes, "The Computer and the Dynamo", American Scientist, Vol 89, No 5, September-October, 2001. pp. 390-394.

- [ITRS05] International Technology Roadmap for Semiconductors, 2005 Edition, available at http://public.itrs.net

- [Iye86] R. Iye, D. Rossetti and M. Hsueh, "Measurement and Modelling of computer reliability as affected by system activity", ACM Trans. On Computer Systems, 4(3):214-237, Aug. 1986.

- [Kaw00] K. Kawamoto, J.G. Koomey, B. Nordman, R.E. Brown, M.A. Piette and A.K. Meier, "Electricity Used by Office Equipment and Network Equipment in the U.S.", Proceedings of the 2000 ACEEE Summer Study on Energy Efficiency in Buildings. Asilomar, CA. August 2000.

- [Kaw01] K. Kawamoto, J.G. Koomey, B. Nordman, R.E. Brown, M.A. Piette, M. Ting and A.K. Meier, "Electricity Used by Office Equipment and Network Equipment in the U.S.: Detailed Report and Appendices", Lawrence Berkeley National Laboratory Internal Report LBNL-45917, University of California. February 2001.

- [Kol01] J. Koliski, R. Chary, A. Henroid and B. Press, "Building the Power-Efficient PC", Intel Press, 2001.

- [Lai01] John A. Laitner, Jonathan Koomey, Ernst Worrell, Etan Gumerman. "Reestimating the Annual Energy Outlook 2000 Forecast Using Updated Assumptions about the Information Economy". Presented at the American Economic Association Conference. New Orleans, LA. January 7 2001. (Also LBNL-46418).

- [Lal97] Pradeep Lall, "Influence of Temperature on Microelectronics and System Reliability", CRC Press, 1997

- [Ped97] M. Pedram, Design technologies for Low Power VLSI, In Encyclopaedia of Computer Science and Technology, Vo. 36, Marcel Dekker, Inc., 1997, pp. 73-96.

- [Rab96] Rabaey, Jan M. "Digital integrated circuits: a design perspective". Upper Saddle River: Prentice-Hall International, 1996.

- [Smi01] Van Smith, "Pentium 4 Thermal Throttling", available at http://www.vanshardware.com.

- [Will99] Craig Willert, "The Evolution of Programmable Logic Design Technology", XCell Journal, Issue 32, 2nd quarter 1999, pp. 5-8.

[XDS06] Xilinx Inc. "Virtex-4 Data Sheet: DC and Switching Characteristics", 2006, available at http://www.xilinx.com

# Chapter 2.

"When we come to design the Ultimate Computers of the far future, which might have "transistors" that are atom-sized, we will want to know how the fundamental physical laws will limit us. When you get down to that sort of scale, you really have to ask about the energies involved in computation, and the answer is that there is no reason why you shouldn't operate below kT". From "Lectures on Computation" by Richard P. Feynman [Fey96].

# **2 VLSI Power Consumption**

This Chapter explains the sources of power dissipation for the CMOS technology. CMOS is (and will remain) the industry workhorse up to and beyond the year 2020 according to ITRS predictions [ITRS2005]. From 2020 it is anticipated new nanoscale devices representing alternatives to CMOS. These new devices will be introduced utilizing different and new ways of processing and storing information. Most of the proposed devices rely on new materials and properties not well studied yet.

The details about the power consumption in FPGAs are particularly specified. Finally, how the activity must be calculated has been carefully studied.

As power optimization is not the topic in this thesis, it is treated briefly in this chapter. A parallel work at our laboratory that presents optimization techniques applicable to SRAM-based FPGAs is [Sut05].

## 2.1 Analysis of Power Consumption

It has been shown that designing VLSI for low power requires a design methodology at every level of the design hierarchy. The main components of such a methodology are estimation and optimization [Lan94], the classical analysis and synthesis pair.

In order to estimate and optimize the power consumption of a digital circuit it is necessary to know how energy is dissipated. The way each factor interacts with the others will also clarify the effects these elements have on every VLSI design stage. This analysis will determine which elements can be overlooked within a specific design environment. Indeed, designing digital circuits with FPGAs requires specific assumptions, as it will be pointed out later on, after a brief discussion on power dissipation sources in CMOS circuits.

#### 2.1.1 Thermodynamics of Computation

Beyond the technological frenzy in the electronic industry nowadays, it is important to stop a moment in order to study the fundamental laws about the power consumption and thermodynamics of computation. In Feynman's book "Lectures on Computation", Chapter 5 [Fey96], two essential questions are studied. The first one is: "How much energy must be used in carrying out a computation?" This thesis explores how much energy will be used in carrying out a computation within a particular technological context: SRAM-based FPGAs, its goal is the estimation of this amount of energy in advance. Nevertheless, the second question is more fundamental: "What is the minimum energy required to carry out a computation?" In this section this second question is considered. Although they are much more efficient than earlier computers, the existing ones dissipate enormous amounts of energy,  $10^8 kT$ , compared with the theoretical lower bound kT (T is the temperature and k is the Boltzman's constant). The main reason for this waste is the use of macroscopic components with relatively huge inertia which require macroscopic amounts of energy to switch quickly. On the other hand, a microscopic device such as DNA replication has relatively high energy efficiency: 20-100kT per operation.

In [Fey96] a physical definition of the information content of a message is studied. In general when we develop an algorithm, we do not think about this but

No computing can be done without the participation of the physical world.

Rolf Landauer, in his classic 1961 paper pioneered applying thermodynamics to computation [Lan61]. In that paper, it is claimed that any logically irreversible computation, such as the erasure of a bit, *must* be accompanied by a corresponding entropy increase; and any logically reversible computation *can* be executed by a thermodynamically reversible device. This is also known as the basic principle of the thermodynamics of information processing or Landauer's principle. His work and other contributions are summarized in [Fey96], where the first conclusion is that the amount of information in a message is proportional to the free energy required to reset the tape to zero. In this way, some energy is necessary to reset a tape with "surprise" bits, but it is interesting to realize that a reset tape also contains energy. Bennet [Ben82] designed a machine that uses such tapes with information as fuel. The tape after that is randomized, full of information and again, some work must be done to reset it. For a detailed study of all these topics, please see the references mentioned in this section. Also interesting is the work in [Ben03], where Landauer's principle is revised and the historic arguments against it are refuted.

The second conclusion in [Fey96] is that ideally, it is possible to operate a computer without any loss of energy. This computation should be done in a reversible computer infinitesimally slowly. The only entropy loss comes in the resetting process for the next operation and does not depend on the complexity of the computation but on the number of output bits *N*:

$$NkT \ln 2$$

(Eq. 2.1)

$kT \ln 2$  is about 3 x 10<sup>-21</sup>J at room temperature. Unfortunately, the price we must pay for this is that we will never know when the computation is finished.

There is not a minimum amount of energy required to carry out a computation, but there is a limit when the computation is done at a certain speed. In this way, the third point studied in [Fey96] is the amount of free energy required to carry out a computation in a finite time. If we have a reversible computer that goes forward at a rate r –it is r times more likely to make a forward computation than a backwards one-then the minimum energy that must be expended per computational step is

$$E_{\rm s min} = kT \ln r \tag{Eq. 2.2}$$

The smaller is *r*, the lower the energy. With some mathematical development, time can be the variable:

$$energy\_loss\_per\_step = kT \frac{min time\_taken\_per\_step}{time\_per\_step\_actually\_taken}$$

(Eq. 2.3)

Again, if the computation is infinitesimally slow, there is no loss of energy.

#### 2.1.2 Sources of Power Dissipation

Beyond the thermodynamic arguments in the previous sections, it is clear that an efficient technology for digital circuit materialization from the power consumption point of view must dissipate the lowest energy possible when some computation is actually performed, and no energy in any other case. This occurs in CMOS circuits (with slight differences with the ideal case) and other modern technologies. Older technologies, such as vacuum tubes and relays dissipate relatively huge amounts of energy —even compared with the CMOS technology, that dissipates relatively enormous amounts of energy compared with the thermodynamic lower bounds- doing some computation or not. Power dissipation in CMOS circuits is caused by three main sources [Ped97]:

- 1. **Leakage** current which is primarily determined by the technology used in its construction, and consists of:

- Reverse bias current in the parasitic diodes formed between source and drain diffusions and the bulk region in a MOS transistor.

- Sub-threshold currents that arise from the inversion charges that exists at the gate voltages below the threshold voltage.

This is also known as static power consumption. In older technologies, with minimum feature size of 0.15  $\mu$ m or larger, adequate design decisions at the physical level may reduce this first source of power dissipation to very low values. However, recent work like [Kao02] suggest that it may represent over 40% of total power at the 70 nm technology. It is also true that, leakage power is proportional to the number of transistors in the off state and FPGAs requires more transistors to implement a logic function than ASICs.

Nevertheless, all these forecasts about power consumption can be interpreted more as a problem statement than a possible future prediction. For example, using triple-oxide technology [Kle05], the overall static power in Virtex-4 devices with 90 nm process is reduced compared to Virtex-II Pro devices with 130 nm process.

- Short-circuit current which is due to the DC path between the supply rails during output transitions,

- 3. **Switching** current: it is dissipated when capacitive loads are charged and discharged during logic changes.

Ideally, a CMOS circuit dissipates no static power since in the steady state there is no direct path from  $V_{dd}$  to ground. Nevertheless, the MOS transistor is not a perfect switch and there will always be parasitic currents. Until now the static current had little effect on the overall power consumption. However, [Li03] found FPGA architectures (with more than 4 inputs in the LUTs) where leakage power emerges as a mayor source of power dissipation in devices using the projected 0.10 um technology.

The short-circuit power consumption, for example in an inverter gate, depends on the gain of the inverter, the supply voltage, the device threshold, the input rise/fall time and the operating frequency. The maximum short-circuit current flows when there is no load; this current decreases with the load.

From Xilinx and Altera datasheets, short-circuit power is 10% of dynamic power. If, however, design for high performance is taken to the extreme where gates with large fanout are used to drive relatively small loads, then there will be an excessive penalty in terms of short-circuit power consumption.

The dominant source of power dissipation is the switching power dissipation and is given, for a circuit node, by:

$$P_i = 0.5 \cdot C \cdot V_{dd}^2 \cdot E(sw) \cdot f_{clk}$$

(Eq. 2.4)

Where:

C is the physical capacitance seen by the gate under consideration,

$V_{dd}$  is the supply voltage,

E(sw) (referred as the switching activity) is the average number of transitions in the circuit per  $1/f_{clk}$  time, and

$f_{clk}$  is the clock frequency.

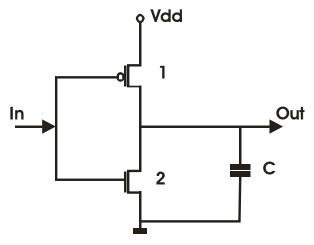

Fig. 2.1. Dynamic power consumption in a CMOS inverter

For a 0  $\rightarrow$   $V_{dd}$  transition, switch 1 is closed (Fig. 2.1), an energy  $E_{0\rightarrow1}=C*V_{dd}^2$  is drawn from the power supply  $V_{dd}$ , and the energy  $E_C=\frac{1}{2}C*V_{dd}^2$  is saved in the capacitance C. The other  $\frac{1}{2}C*V_{dd}^2$  is dissipated in transistor 1.

For a  $V_{dd} \rightarrow 0$  transition, switch 2 is closed, no energy is drawn from  $V_{dd}$ , but the energy previously stored in C is dissipated [Guy98] in transistor 2.

#### 2.1.2.1 Extending the Dynamic Power Formula

Firstly, in [Li03] a simple model is proposed in order to consider the short-circuit power within Eq. 2.2. This component also depends on the switching activity. It can be assumed that the ratio between short-circuits and switching power,  $R_{sc}$  is a constant. In this way, an effective capacitance is defined as follows:

$$\hat{C} = C(1 + R_{sc})$$

(Eq. 2.5)

$\hat{C}$  is the total equivalent capacitance connected to the output of the gate under consideration. In this way, the short-circuit component can be integrated together with the charging and discharging of the node capacitances. These two power components are referred to as dynamic power dissipation.

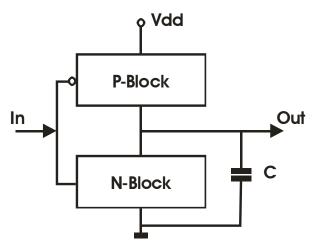

Another point to consider is that Eq. 2.2 is obtained for a CMOS inverter, but the same results can be dragged for other logic gates and MOSFET based circuits. The only difference between the inverter and other CMOS gates, in order to calculate the load capacitance, is the number of transistors in each complementary part (Fig. 2.2).

Fig. 2.2: Dynamic power consumption in a generic CMOS gate

For the whole circuit, the power can be calculated adding up all the contributions:

$$P = \frac{1}{2} V_{dd}^2 f_{clk} \sum_{i} \hat{C}_i E(sw)_i$$

(Eq. 2.6)

It should be noted that in some work in this area, the 0.5 factor does not appear in the formula. In these cases the switching activity is replaced by the effective frequency. The effective number of signal cycles doubles the number of signal transitions.

The last point studied in this section, related to Eq. 2.3, is that it only considers full swings between  $V_{dd}$  and GND. Short glitches have partial swings and are considered by  $\hat{E}(sw)_i$ , the effective switching activity.

$$P = \frac{1}{2} V_{dd}^2 f_{clk} \sum_{i} \hat{C}_i \hat{E}(sw)_i$$

(Eq. 2.7)

Details of  $\hat{E}(sw)_i$  and  $\hat{C}_i$  estimation are explained in Chapter 5.

## 2.2 Power Consumption in FPGAs

The previous section exposes the three variables, and degrees of freedom, inherent in the low-power design space: voltage, physical capacitance, and data activity. Because of the quadratic relationship to the power, voltage reduction offers the most effective means to minimize power consumption. Furthermore, this power reduction has a global effect, experienced not only in one gate or circuit node, but throughout the sub-circuit or device supplied with the same voltage. However, programmable logic devices are studied in this work. Once a specific commercially available device is selected, the nominal power supply voltages are given in the data sheets and only capacitance and switching activity need to be estimated (and optimized).

FPGAs consume much more power than ASICs because they have a large number of transistors per logic function in order to program the device. Nevertheless, programmability is the essence of this technology and this overhead must be assumed. In this section the different electronic components of a SRAM-based FPGA are analyzed in order to determine whether or not Eq. 2.4 can be applied to all the nodes in any design.

Most of the models used to explain the power consumption behavior of SRAM-based FPGAs are based on the equations derived from the analysis of the CMOS inverter. As it was said before, an efficient technology would dissipate the lowest energy when some computing is actually performed, while no energy is dissipated in any other case. SRAM-based FPGAs, like the ones used in this work as technological framework, have pure CMOS circuits but also pass-transistor structures, SRAM, buffers, input and output circuits [Gar00].

As it is presented in [Rab96b] (See chapter 3 by C. Svensson and D. Liu), the combinational CMOS static logic is the selected technology for low power. Though, for timing control in synchronous circuits, simple, non-precharged, dynamic flip-flops, or static gate based flip-flops appear to be the best suited techniques. It is important to note that, in the case of flip-flops, there is a component of the dynamic power consumption that does not depend on the input activity and thus behaves like static power consumption. This is the power consumed by transistors clocked at their gates. The power consumption for a non-precharged TSPC flip-flop is:

$$P_d = (8C_i + 4C_o + 4(\alpha/2)C_i + 8\alpha C_o) f V_{dd}^2$$

(Eq. 2.8)

The first two terms do not depend on the input activity.  $C_i$  and  $C_o$  are respectively the input and output capacitances at the transistors and  $\alpha$  is the data activity.

Another problem found in logic circuits and in particular in FPGAs, comes from the high capacitance nodes where drivers are used to decrease the delay and the short-circuit power consumption due to long rise and fall times in the following stages. As shown in [Rab96b], using a tapered inverter chain, and minimizing the delay, the driver causes an excess power consumption of 80% over the load.

### 2.2.1 Programmable Routing

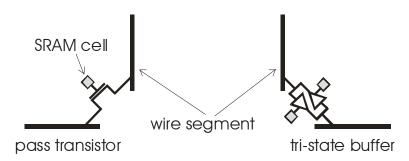

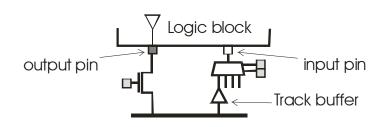

[Bet99] describes two important circuits in the design of FPGA routing switches: pass transistors and tri-state buffers. Routing switches are either pass transistors or pairs of tri-state buffers (one in each direction), and allow routing wire segments to be joined to form longer connections (Fig 2.3). Multiplexers allow routing wires to be connected to the input pins of logic blocks, while demultiplexers (a set of pass transistors) allow routing wires to be driven by output pins of logic blocks (Fig. 2.4).

Fig. 2.3: Routing Switch

Fig. 2.4: Logic Block Routing

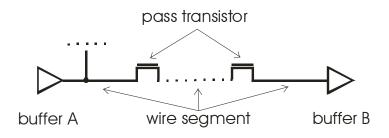

Pass transistors connecting different wire segments can be modeled by equivalent resistances and capacitances. In this way, it is possible to lump together the capacitances of wire segments and pass transistors in a net or node. In other words, these transistors are considered part of the wire. Buffers can be treated as logic cells and the wires, including pass transistors, are driven by these buffers. For example, Fig. 2.5 shows a net composed by several wire segments and pass transistors from buffer A to buffer B.

Fig. 2.5: Net or node model

### 2.2.2 Physical Capacitance

Interconnection plays a prominent role in determining the total chip area, delay and power, and hence, must be accounted for as early as possible during the design process. In the particular case of FPGAs, the long routing tracks, with significant capacitance, consumes relatively a lot of power for every transition. For example, [Poo02] [Poo05] found for theoretical models that 57% of the total energy consumption is due to connections between the logic clusters.

Power dissipation is linearly dependent on the physical capacitances driven by individual gates. So, once a design is mapped, placed and routed in a specific technology, capacitance calculation could be easily done using information from the target library. Unfortunately, this is not the case for commercial FPGAs: often, manufacturers do not provide the information about internal nodes capacitance or at least they do not give it directly. This makes mandatory the development of a solution in this thesis for the capacitance retrieval problem and it is presented in Chapter 6.

### 2.2.3 Switching Activity

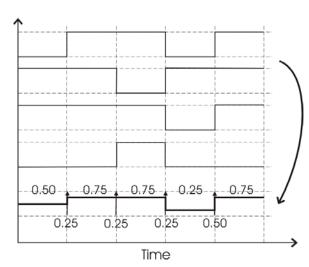

In addition to voltage and physical capacitance, switching activity is the third factor that determines the dynamic power consumption. A chip may contain a high amount of physical capacitance, but if there is no switching in the circuit, then no dynamic power will be consumed. In a combinational circuit, if two consecutive and identical vectors are presented at the circuit inputs, no power is dissipated. The data activity determines how often this switching occurs. There are two components to the switching activity:

- 1.  $f_{clk}$  which determines the average periodicity of data arrivals, and

- 2. *E(sw)* which determines how many transitions each data arrival will generate.

$F_{clk}$  and E(sw) are strongly related.  $F_{clk}$  can not be unlimitedly increased. The corresponding signal must have enough time,  $1/f_{clk}$ , to reach the steady state before the arrival of the new input vector.

For circuits that do not experience glitching, E(sw) can be interpreted as the probability that a power consuming transition will occur during a single data period. Even for these circuits, calculation of E(sw) is difficult as it depends not only on the switching activities of the circuit inputs and the logic function computed by the circuit, but also on the spatial and temporal correlations among the circuit inputs.

For certain design styles, glitching can be an important source of signal activity. Glitching refers to spurious and unwanted transitions that occur before a node settles down to its final steady-state value. Glitching often arises when paths with unbalanced propagation delays converge at the same point in a circuit. Since glitching can cause a node to make several unnecessary power consuming transitions, it should be avoided whenever possible [Boe95].

The data activity E(sw) can be combined with the physical capacitance C to obtain switched capacitance,  $C_{sw} = C.E(sw)$ , which describes the average capacitance charged during each data period  $1/f_{c/k}$ . It is a useful magnitude for comparing implementations running at different clock frequencies and with different voltages.

## 2.3 Switching Activity Computation

The computing of switching activity in a logic circuit is difficult because it depends on a number of parameters. Some of these parameters are technology-dependent factors and will be treated below. The input pattern dependence, the delay model at each design stage, the circuit logic function and, for some techniques, the circuit structure, are not technology-dependent factors. The impact of these factors on the circuit node activity will be illustrated in the following sections.

### 2.3.1 Dependence on the Input Patterns

| N  | Input I | Input J | Output | Tr |

|----|---------|---------|--------|----|

| 1  | 0-0     | 0-0     | 0-0    | Z  |

| 2  | 0-0     | 0-1     | 0-0    | Z  |

| 3  | 0-0     | 1-0     | 0-0    | Ν  |

| 4  | 0-0     | 1-1     | 0-0    | N  |

| 5  | 0-1     | 0-0     | 0-0    | N  |

| 6  | 0-1     | 0-1     | 0-1    | Υ  |

| 7  | 0-1     | 1-0     | 0-0    | N  |

| 8  | 0-1     | 1-1     | 0-1    | Υ  |

| 9  | 1-0     | 0-0     | 0-0    | N  |

| 10 | 1-0     | 0-1     | 0-0    | N  |

| 11 | 1-0     | 1-0     | 1-0    | Υ  |

| 12 | 1-0     | 1-1     | 1-0    | Υ  |

| 13 | 1-1     | 0-0     | 0-0    | N  |

| 14 | 1-1     | 0-1     | 0-1    | Υ  |

| 15 | 1-1     | 1-0     | 1-0    | Υ  |

| 16 | 1-1     | 1-1     | 1-1    | N  |

Table 2.1: Activity for an AND gate with independent inputs

For example, consider a two-input AND gate g with independent inputs I and J whose signal probabilities are  $\frac{1}{2}$ , then Eg (sw) = 3/8. This holds because in 6 out of 16 possible input transitions, the output of the two-input AND gate makes a transition as is shown in Table 2.1.

Now suppose that it is known that only patterns 00 and 11 can be applied to the gate inputs and that both patterns are equally probable, then  $E_g(sw)=1/2$  (Table 2.2).

| N | Input I | Input J | Output | Tr |

|---|---------|---------|--------|----|

| 1 | 0-0     | 0-0     | 0-0    | Z  |

| 2 | 0-1     | 0-1     | 0-1    | Υ  |

| 3 | 1-0     | 1-0     | 1-0    | Υ  |

| 4 | 0-0     | 1-1     | 0-0    | Ν  |

Table 2.2: Activity for an AND gate with spatial dependence among the inputs

Alternatively, if one assumes that it is known that every 0 applied to input I is immediately followed by a 1, while every 1 applied to input J is immediately followed by a 0, then  $E_g(sw) = 4/9$  (Table 2.3).

| N | Input I | Input J | Output | Tr |

|---|---------|---------|--------|----|

| 1 | 0-1     | 0-0     | 0-0    | Z  |

| 2 | 0-1     | 0-1     | 0-1    | Υ  |

| 3 | 0-1     | 1-0     | 0-0    | Z  |

| 4 | 1-0     | 0-0     | 0-0    | Z  |

| 5 | 1-0     | 0-1     | 0-0    | Z  |

| 6 | 1-0     | 1-0     | 1-0    | Υ  |

| 7 | 1-1     | 0-0     | 0-0    | Z  |

| 8 | 1-1     | 0-1     | 0-1    | Υ  |

| 9 | 1-1     | 1-0     | 1-0    | Υ  |

Table 2.3: Activity for an AND gate with temporal dependence among the inputs

Finally, if one assumes that it is known that I changes whenever J changes its value, then  $E_g(sw) = \frac{1}{4}$  (see Table 2.4).

| N | Input I | Input J | Output | Tr |

|---|---------|---------|--------|----|

| 1 | 0-0     | 0-0     | 0-0    | N  |

| 2 | 0-0     | 1-1     | 0-0    | Ν  |

| 3 | 0-1     | 0-1     | 0-1    | Υ  |

| 4 | 0-1     | 1-0     | 0-0    | N  |

| 5 | 1-0     | 0-1     | 0-0    | N  |

| 6 | 1-0     | 1-0     | 1-0    | Υ  |

| 7 | 1-1     | 0-0     | 0-0    | Ν  |

| 8 | 1-1     | 1-1     | 1-1    | N  |

Table 2.4: Activity for an AND gate with spatial-temporal dependence among the inputs

The first case is an example of spatial correlations between gate inputs; the second case illustrates temporal correlations; while the third case describes an instance of spatial-temporal correlations.

In general there are first order and higher order temporal correlations. In the first case the next value of a signal depends on its current value. In the second case it also depends on the n previous values.

There are also special names for some types of correlations for internal signals. Spatial, temporal and spatial-temporal correlations at state lines, induced by a finite state machine, are known as sequential correlations. Even if primary inputs are uncorrelated, the state lines can be strongly correlated. Another interesting case of spatial correlation in internal signals is due to reconvergent fanout known as structural correlations. Reconvergent nodes are explained below in this Chapter. A very interesting study of the effects of correlations on power estimation methods is presented in [Sch96a].

With the previous examples, it is clear that the straightforward approach of estimating power just by using a simulator and applying a big but arbitrary set of input patterns may give erroneous results due to this pattern-dependence problem. Experiments that quantify this fact are presented in this thesis.

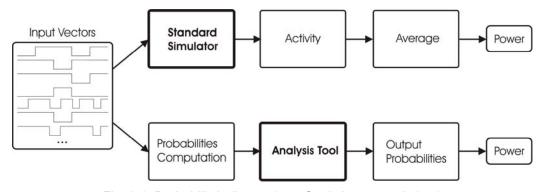

It is clearly unfeasible to estimate the power consumption by exhaustive simulation of the circuit. Even for a combinational circuit with n inputs, it is not enough to apply the  $2^n$  combinations because the activity depends on the node state after the last applied vector. In the restrictive case of uniform distribution, the number of combinations is  $2^{2n}$ . Some techniques have been proposed to overcome this difficulty by using probabilities that describe the set of possible logic values at the circuit inputs. Some mechanisms to calculate these probabilities for gates inside the circuit have also been proposed. Alternatively, exhaustive simulation may be replaced by Monte-Carlo simulation with well-defined stopping criterion for specified relative or absolute error in power estimates and a given confidence level [Naj98]. A survey of activity estimation techniques will be presented in Chapter 3.

## 2.3.2 Delay Model

Any power estimation techniques must account for steady-state transitions (which consume power and are necessary to perform a computational task). Based on the used delay model also the glitches could be considered (which dissipate power without doing any useful computation). Sometimes, the first component of power consumption is referred to as the functional activity while the latter is referred to as the spurious activity. It is shown in Chapter 5 that the average number of transitions per clock cycle in a combinational multiplier reaches high values in some nodes. The spurious power dissipation may be more significant in FPGAs than in ASICs because of the relative importance of the nets [Sha02].

Current power estimation techniques often handle both zero-delay (non-glitch) and real delay models. In the first model, it is assumed that all changes at the circuit inputs propagate through the internal gates of the circuits instantaneously. The latter model assigns a finite delay to each gate in the circuit and can thus account for the hazards in the circuit. A real delay model, post P&R, increases the computational requirements of the power estimation techniques while improving the accuracy of the estimates. On the other hand, support for the zero-delay models is useful for power estimation in early stages of the design process. Furthermore, between these two simulation models,

there are others coming from different points in the design flow (post synthesis, technology mapping, and place). The closer the simulation model is to the post P&R version, the more accurate could be the estimation.

The computing of spurious activity requires careful logic and circuit level characterization of the gates in a library as well as detailed knowledge of the circuit structure. This means that different results will be obtained if the estimation is done using a model generated before the technology mapping, when no technological data may be taken into account and no timing information is available; or after the technology mapping, when timing information is available just for the logic but not for the nets; or after the place and route, when a complete timing information is available.

VHDL users know how to write abstract, technology independent descriptions, but now it is necessary to simulate the actual hardware. How can such a simulation be done? The answer is VITAL (IEEE 1076.4 standard) [VIT01]. The VITAL (VHDL Initiative Towards ASIC Libraries) is a modeling specification that defines a methodology which promotes the development of highly accurate, efficient simulation models for ASIC components in VHDL.

## 2.3.2.1 The IEEE VITAL Standard

The way to describe "physical" hardware in VHDL is to write VHDL models of those components. This is supported in VHDL through the use of instantiation. Historically, gate-level simulation using VHDL has been notoriously slow. This led to the creation of the 1076.4 working group to provide a mechanism to allow fast gate-level simulation using VHDL. Their effort became known as the VITAL standard. VITAL is not an issue for VHDL designers, but an EDA vendor/ASIC supplier issue. A simulator is VITAL compliant if it implements the VITAL package in its kernel.

The FPGA vendor's library elements need to be implemented entirely in VITAL primitives. They also provide tools that generate these VHDL models from post map, P&R, etc. proprietary files. Also note that, with the VHDL model, a SDF (Standard Delay Format) file [SDF01] is generated. The SDF file contains timing data and the VITAL compliant simulator, having implemented an SDF reader, directly imports it into the simulator. The naming conventions and types of VITAL generics provide the placeholders to load timing data via back-annotation.

Although an SDF file specifies delays as min:typ:max values, only one of these values will be used for back-annotation. The selection of the specific delay values (min, typ or max) could be done by the back-annotation program under a user controlled option.

## 2.3.3 Logic Function

In the first place, switching activity at the output of a logic gate depends on the Boolean function of the gate itself. For example, under the assumption that the input signals are uncorrelated, switching activity at the output of a two-input NAND or NOR gate is 3/8 and at the output of a two-input XOR gate is ½ (see Table 2.5).

| N  | Input I | Input J | Output | NAND | NOR | XOR |

|----|---------|---------|--------|------|-----|-----|

| 1  | 0-0     | 0-0     | 0-0    | N    | N   | N   |

| 2  | 0-0     | 0-1     | 0-0    | N    | Υ   | Υ   |

| 3  | 0-0     | 1-0     | 0-0    | N    | Υ   | Υ   |

| 4  | 0-0     | 1-1     | 0-0    | N    | N   | Ν   |

| 5  | 0-1     | 0-0     | 0-0    | N    | Υ   | Υ   |

| 6  | 0-1     | 0-1     | 0-1    | Υ    | Υ   | N   |

| 7  | 0-1     | 1-0     | 0-0    | N    | N   | Ν   |

| 8  | 0-1     | 1-1     | 0-1    | Υ    | N   | Υ   |

| 9  | 1-0     | 0-0     | 0-0    | N    | Υ   | Υ   |

| 10 | 1-0     | 0-1     | 0-0    | N    | N   | Ν   |

| 11 | 1-0     | 1-0     | 1-0    | Υ    | Υ   | Ν   |

| 12 | 1-0     | 1-1     | 1-0    | Υ    | N   | Υ   |

| 13 | 1-1     | 0-0     | 0-0    | N    | N   | N   |

| 14 | 1-1     | 0-1     | 0-1    | Υ    | N   | Υ   |

| 15 | 1-1     | 1-0     | 1-0    | Υ    | N   | Υ   |

| 16 | 1-1     | 1-1     | 1-1    | N    | N   | N   |

Table 2.5: Activity for different logic gates

Indeed, switching activity at the output of a K-input NAND or NOR gate approaches  $\frac{1}{2}^{K-1}$  for large K whereas that for a K-input XOR gate remains at  $\frac{1}{2}$ . The proposition for a K-input NAND gate can be demonstrated as follows.

As mentioned, the number of input vector combinations, when activity is studied at a gate or circuit output, is  $2^{2K}$ , being K the number of primary inputs. In order to analyze a K-input NAND gate, all the combinations can be arranged in groups. In each group the first K-input vector is kept fixed, and for the second k-input vector has  $2^{K}$  combinations. In all but one group there is just one case where a 1 to 0 transition is generated, when the second vector is formed by all 1's. The exceptional group is the one with the fixed vector with all 1's, where the possible transition is from 0 to 1. This happens in all the cases in the group except when the second vector is also the one formed by all 1's, keeping the gate output at logic 0.

Then, there are  $2^K-1$  groups with one transition, and one group with  $2^K-1$  transitions. The transition probability for the NAND gate where the inputs are independent is:

$$P(NAND_{K}) = \frac{(2^{K} - 1) + (2^{K} - 1)}{2^{2K}} = \frac{2^{K+1} - 2}{2^{2K}}$$

(Eq. 2.9)

If *K* is big enough the second constant term can be neglected, then:

$$P(NAND_K) \cong \frac{2^{K+1}}{2^{2K}} = 2^{K+1-2K} = 2^{-K+1} = \frac{1}{2^{K-1}}$$

(Eq. 2.10)

The demonstration for the K-input NOR gate can be developed in the same way.

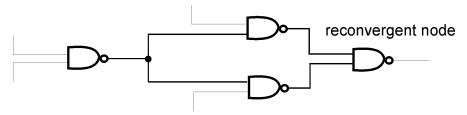

#### 2.3.4 Circuit Structure

If probabilistic techniques are used to estimate the switching activity, probabilities are calculated and propagated from primary inputs to the inner nodes and finally, to the circuit outputs. But dependencies among the inputs complicate probability calculations. Although primary inputs were supposed uncorrelated other dependencies originated on the circuit structure remain: the reconvergent nodes, circuit nodes that receive inputs from two paths connected to some gate output (Fig. 2.6). If a network consists of simple gates and has no reconvergent fan out nodes, then the exact switching activities can be computed during a single post-order traversal of the network [Ped94]. For

networks with reconvergent nodes, the problem is much more challenging, as internal signals may become strongly correlated and exact consideration of these correlations cannot be performed with reasonable computational effort or memory usage. Current power estimation techniques either ignore these correlations or approximate them, thereby improving the accuracy at the expense of longer run times. Exact methods (i.e., symbolic simulation) have also been proposed, but are impractical due to excessive time and memory requirements.

Fig. 2.6: Example of a reconvergent node

### 2.3.5 Technology-dependant Factors

In actual networks, statistical perturbations of circuit parameters may change the propagation delays and produce changes in the number of transitions because of the appearance or disappearance of glitches. For that reason it is useful to determine the change in the signal transition count as a function of these statistical fluctuations.

Variation of gate delay parameters may change the number of glitches occurring during a transition as well as their duration. In this way, the spurious component of power dissipation is sensitive to IC parameter fluctuations [Ben94].

### 2.4 Conclusions

The need for lower power systems is crucial in electronic applications from portable devices to high-end computers. Nevertheless, designing for low power adds another dimension to the already complex VLSI design problem: the design has to be optimized for power as well as for performance and area.

Optimizing these three axes necessitates a new generation of EDA tools at all design phases. These power aware tools and methodologies include power estimation tools. Behavioral synthesis, logic synthesis and layout optimization tools require

accurate and efficient estimation of the power consumption of alternative implementations.

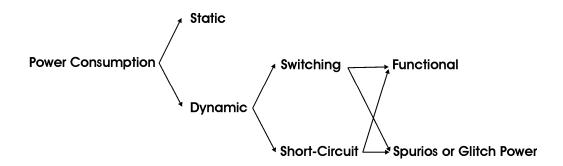

There are several sources of power consumption in CMOS circuits (Fig. 2.7) but the dynamic power is the main component. In order to estimate the dynamic power consumption, both activity and capacitance must be gauged. Activity is hard to estimate because its dependence on the input patterns (known as the pattern-dependence problem). Nevertheless, the capacitance recovery is a specific design problem for commercial FPGAs because of the lack of these data or any direct information about how to calculate the capacitance at each circuit node.

Fig. 2.7. Sources of power consumption in CMOS circuits and FPGAs

### References

- [Ben03] Charles H. Bennett, "Notes on Landauer's Principle, Reversible Computation and Maxwell's Demon", Studies in History and Philosophy of Modern Physics, v. 34, pp. 501-510, 2003.

- [Ben82] C.H. Bennett, "The Thermodynamics of Computation a Review" Internat. J. Theoret. Phys. 21, pp. 905-940 (1982).

- [Ben94] L. Benini, M. Favalli, and B. Ricco, "Analysis of hazard contribution to power dissipation in CMOS IC's". In Proceedings of the 1994 International Workshop on Low Power Design, pp 27-32, April 1994.

- [Bet99] Vaughn Betz and Jonathan Rose, "Circuit Design, Transistor Sizing and Wire Layout of FPGA Interconnect", IEEE Custom Integrated Circuits Conference, 1999.

- [Boe95] Boemo, E., Gonzalez de Rivera, G., Lopez-Buedo, S., Meneses, J., "Some Notes on Power Management on FPGAs", LNCS, No. 975, Springer-Verlag, Berlin (1995) 149-157.

- [Fey96] Richard P. Feynman, "Feynman Lectures on Computation", Ed. A.J.G. Hey and

- R.W. Allen. Addison-Wesley, 1996.

- [Gar00] Andrés David García García, "Etude sur l'Estimation et l'Optimisation de la consommation de puissance", PhD Thesis, l'Ecole Nationale Supérieure des Télécommunications, Paris, 2000.

- [Guy98] Alain Guyot and Sélim Abou-Samra, "Low Power CMOS Digital Design", In proc. Of International Conference on Microelectronics 1998 (ICM'98), Monastir, Tunisia, December 1998.

- [ITRS04] ITRS Technology Working Group, "Overall Roadmap Technology Characteristics (ORTC)", from the International Technology Roadmap for Semiconductors (ITRS). 2004 Upgrade. Available at http://public.itrs.net

- [Kao02] James Kao, Siva Narendra, Anantha Chandrakasan, "Subthreshold leakage modeling and reduction techniques", In proc. of the 2002 IEEE/ACM international conference on Computer-Aided Design, pp. 141-148, 2002

- [Kle05] M. Klein, "The Virtex-4 Power Play", Xcell Journal, Spring 05

- [Lan61] R. Landauer, "Irreversibility and Heat Generation in the Computing Process", IBM Journal of Research and Development, Vol 5, N 3, pp. 261-269, 1961.

- [Lan94] P. Landman, Low-Power Architectural Design Methodologies, Ph. D. Thesis, Electronic Research Laboratory, University of California, Berkeley, August 1994.

- [Li03] Fei Li, Deming Chen, Lei He, Jason Cong: "Architecture evaluation for power-efficient FPGAs", Proc. Of Int. Symp on Field Programmable Gate Arrays, 2003, pp. 175–184

- [Naj98] F. N. Najm and M. G. Xakellis, "Statistical estimation of the switching activity in VLSI circuits", VLSI Design, vol. 7, no. 3, pp. 243-254, 1998.

- [Ped94] M. Pedram, "Power estimation and optimization at the logic level," Int'l Journal of High Speed Electronics and Systems, Vol. 5, No. 2 (1994), pp. 179-202.

- [Ped97] M. Pedram, "Design technologies for Low Power VLSI", In Encyclopaedia of Computer Science and Technology, Vo. 36, Marcel Dekker, Inc., 1997, pp. 73-96.

- [Poo02] Kara K.W. Poon, Andy Yan, Steven J.E. Wilton, "A Flexible Power Model for FPGAs", LNCS, Volume 2438, Jan 2002, pp. 312-321.

- [Poo05] Kara K.W. Poon, Steven J.E. Wilton, and A. Yan, "A Detailed Power Model for Field-Programmable Gate Arrays," ACM Transactions on Design Automation of Electronic Systems (TODAES), vol. 10, issue 2, pp. 279-302, April 2005.

- [Rab96b] Jan M. Rabaey and Massoud Pedram. "Low power design methodologies". Boston, Kluwer Academic, 1996.

- [Sch96a] P. Schneider and S. Krishnamoorthy. "Effects of correlations on accuracy of power analysis an experimental study", International Symposium on Low Power Electronics and Design, Monterey, California, United States, 1996, pp. 113-116.

- [SDF01] IEEE Std 1497-1999, IEEE Standard for Standard Delay Format (SDF) for the Electronic Design Process. The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA, 2001.

- [Sha02] L. Shang, A. S. Kaviani, K. Bathala, "Dynamic Power Consumption in Virtex-II FPGA Family", FPGA 2002 Monterey, California, USA, February 24-26, 2002,

pp. 157-164.

[Sut05] Gustavo Sutter, "Aportes a la Reducción de Consumo en FPFAs", Ph. D. Thesis, Departamento de Ingeniería Informática, Escuela Politécnica Superior, Universidad Autónoma de Madrid, April 2005.

[VIT01] IEEE Std 1076.4-2000, IEEE Standard for VITAL ASIC (Application Specific Integrated Circuit) Modelling Specification. The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA, 2001.

## Chapter 3.

"If it (the author refers to questionable estimations about power consumption of computer equipment in the USA) were correct, we are approaching a notable inflection point in human affairs, where we expend as much effort in moving information as we do in moving matter." From "The Computer and the Dynamo" by Brian Hayes [Hay01]

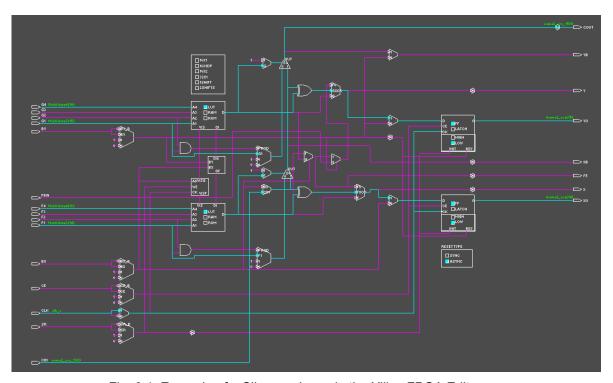

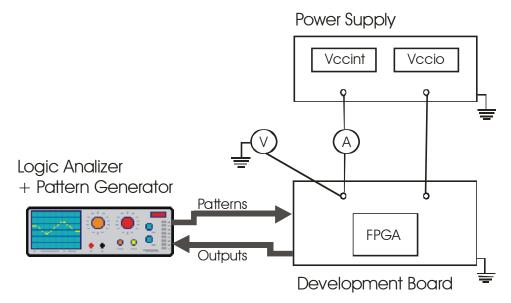

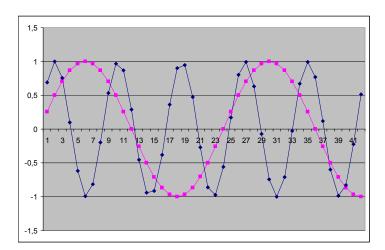

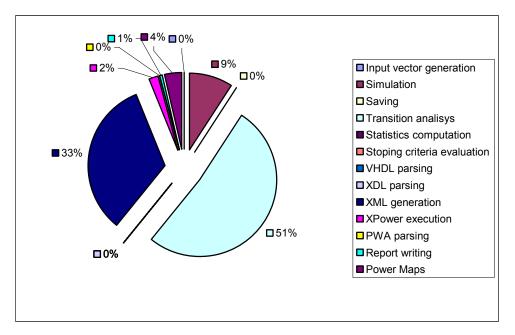

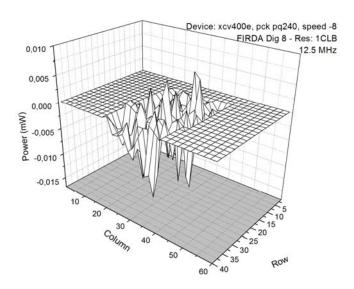

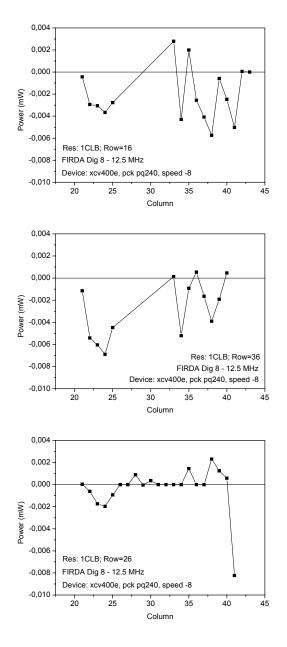

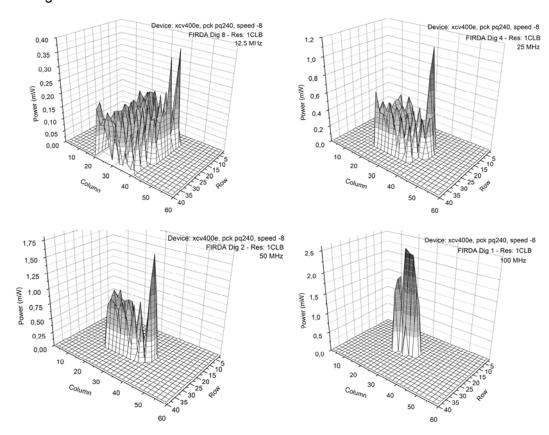

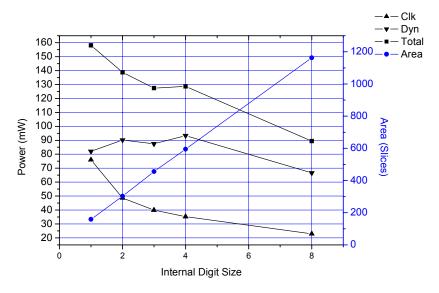

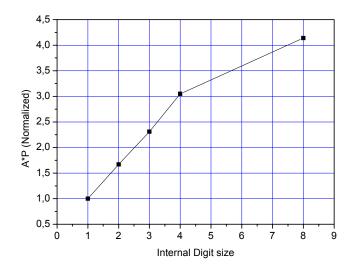

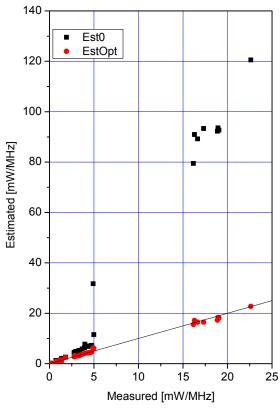

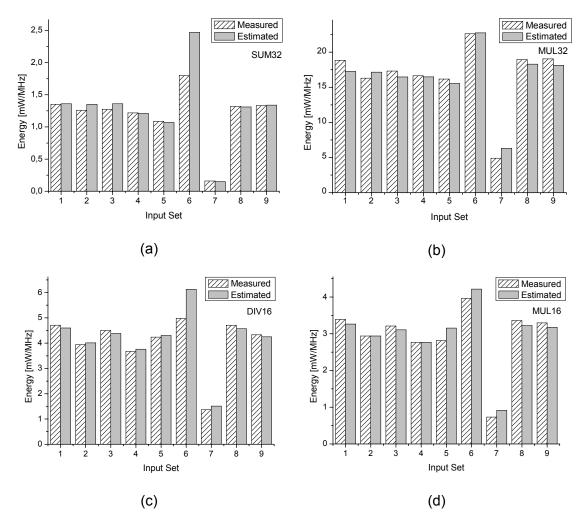

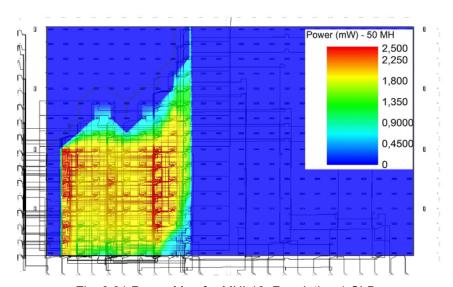

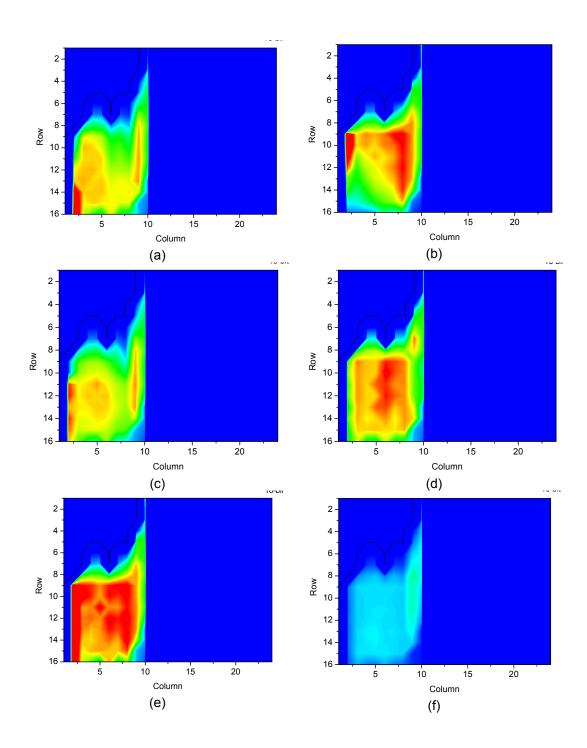

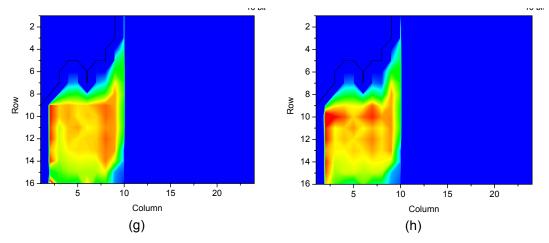

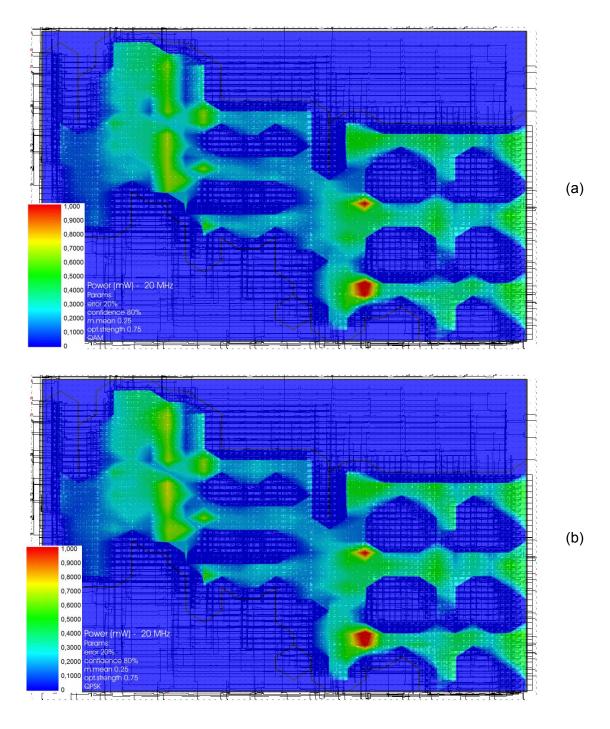

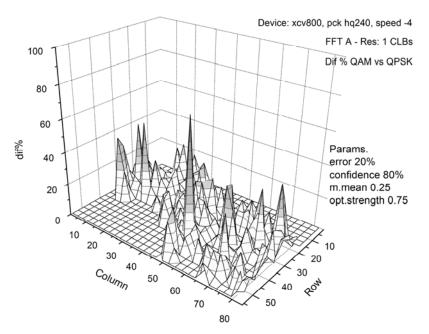

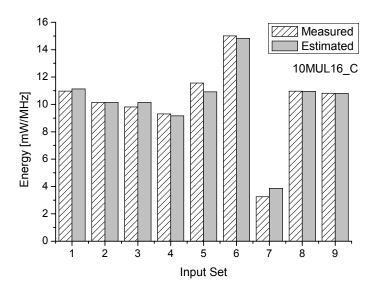

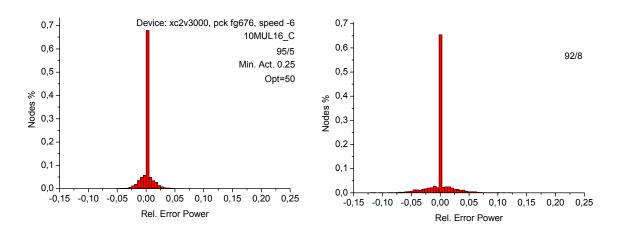

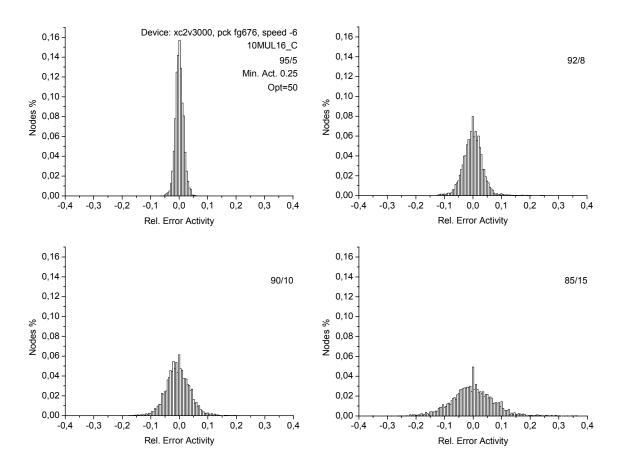

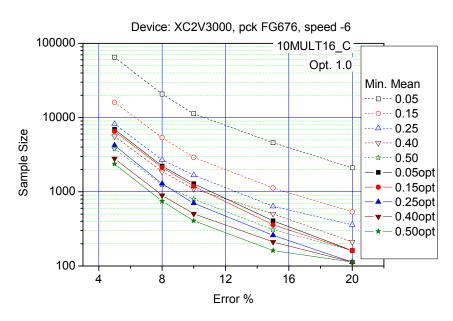

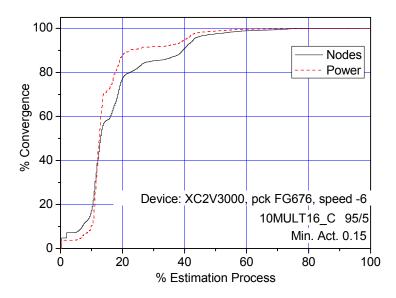

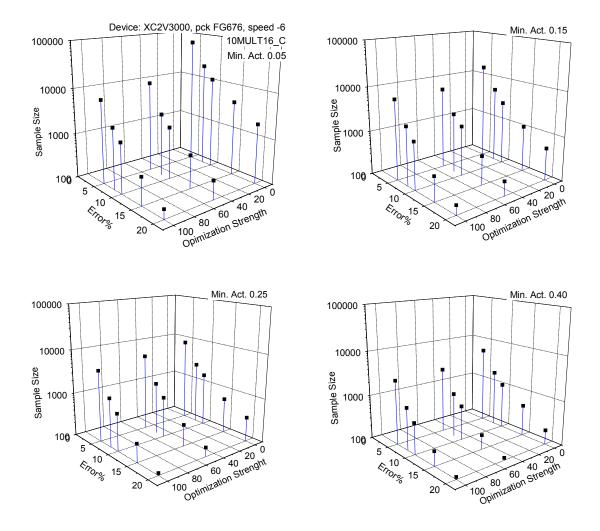

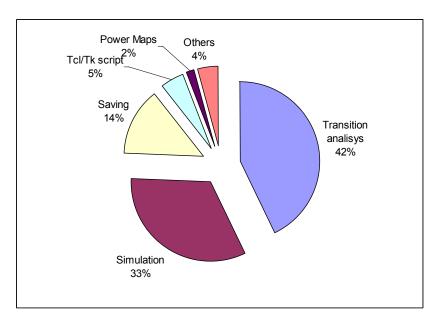

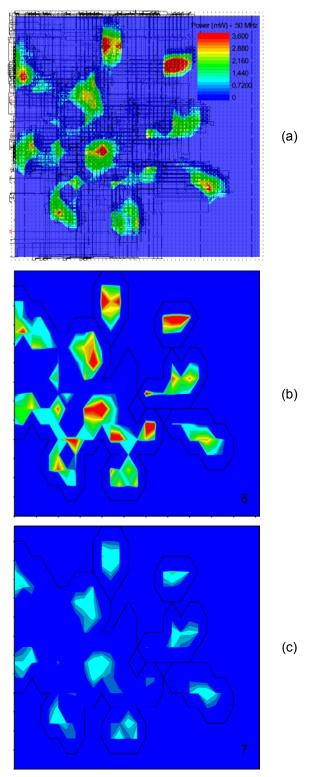

## 3 Power Estimation Techniques