# Exploring strategies to improve FPGA design with higher levels of abstraction

By

# TOBÍAS ALONSO PUGLIESE

PH.D. THESIS

# UNIVERSIDAD AUTÓNOMA DE MADRID

# ESCUELA POLITÉCNICA SUPERIOR

Departamento de Tecnología Electrónica y de las Comunicaciones

Ph.D. Advisors: Dr. Gustavo Sutter Capristo Dr. Jorge E. López de Vergara Méndez

MADRID, MAY 2022

A mi Luky, quien todos estos años ha estado siempre a mi lado.

#### ABSTRACT

While our data processing needs continue to grow at a fast pace, the capacity of general purpose hardware to increase their compute power is decreasing with each successive technology generation. Then, it becomes more important to resort to other means to improve performance. Custom designed hardware, in particular, implemented in FPGAs, has been a vital tool in many application areas and, under the current circumstances, it might be essential to push performance forward. In this context, this thesis explores strategies that can be used in the different hardware design stages to enhance performance of custom-designed solutions using FPGAs and the ability of hardware designers to tackle larger hardware design problems. The work is focused on three application areas, image processing, network packet processing and artificial intelligence, where system requirements and design challenges are analyzed, and later addressed, proposing solutions.

In the area of image processing, we tackle compression under stringent constraints, like those faced in satellite and drone sensing. Given that available image compression algorithms do not properly address the problems in these scenarios, an algorithmhardware co-design approach was followed. We proposed a series of enhancements to the JPEG-LS standard, aimed at improving its coding efficiency at a low computational overhead, and later, developed an FPGA implementation of the encoder. As a result, a low latency near-lossless compressor with the highest pixel rate and highest compression ratio was achieved, outperforming existing implementations.

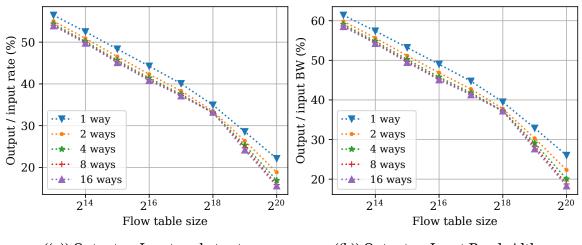

In the area of network packet processing, we focus on the problem of offloading the flow metering process for 100 Gbit Ethernet. Although for slower link rates a highlevel synthesis implementation can provide a solution, for the target link and relevant applications that require managing large memories, this route was insufficient. For this reason, an alternative architecture was designed to address the problem of implementing high-throughput and complex read-update processes dealing with significant propagation delays associated with the memory system. This allowed to implement in an FPGA a TCP flow metering system supporting 100GbE packet rate and achieving over a 50% offload of the computational load. We also demonstrate that using arrays of the developed cores enable the use of larger flow tables, increasing the offloading capabilities, while still supporting the maximum packet rate.

In addition, we studied a complementary throughput optimization for read-update processes, the conditional stalling technique. We concluded that, with efficient implementations, its utilization will not have frequency penalties for most designs and that few extra resources are required. Also, we examined the performance of the technique as a function of input data and architecture characteristics, showing that, even in adverse cases, it can significantly enhance performance. However, we demonstrated that to optimize throughput, we must take into account both the memory address statistics and the evolution of frequency as the pipeline is deepened.

In the area of artificial intelligence, we deal with a set of related implementation problems that arise when scaling up convolutional neural network dataflow accelerators, in particular in non-monolithic (multi-SLR) FPGAs. To tackle them, we developed a partitioning and resource balancing optimization tool. This tool addresses the control signals connection of large designs in multi-SLR FPGAs, and balances multiple resources across FPGA regions and/or chips, while it minimizes the communication cost among them. The tool natively maps systems to a multi-node implementation if it does not fit in a single FPGA, and supports different multi-node paradigms. The application of this optimization significantly enhanced performance of the accelerators. Targeting multi-node platforms led to further compute density, latency and power improvements.

Finally, from the experience obtained in the development of these applications, we identified key methodological aspects that led us to a successful hardware implementation using high-level synthesis (HLS). In particular, we observed that HLS can achieve great quality of results, leveraging wider algorithmic exploration and function specialization. Also, we identify the benefits of modular partitioning and refinement, and using a hardware oriented development mentality.

#### RESUMEN

Mientras nuestras necesidades de procesamiento de datos siguen creciendo a gran velocidad, la capacidad del hardware de propósito general para aumentar su potencia de cálculo va disminuyendo con cada generación tecnológica sucesiva. Entonces, se hace más importante recurrir a otros medios para mejorar el rendimiento. El hardware diseñado a medida, en particular, implementado en FPGAs, ha sido una herramienta vital en muchas áreas de aplicación y, en las circunstancias actuales, puede ser esencial para impulsar el rendimiento. En este contexto, esta tesis explora las estrategias que se pueden utilizar en las diferentes etapas de diseño de hardware para mejorar el rendimiento de las soluciones diseñadas a medida utilizando FPGAs y la capacidad de los diseñadores de hardware para abordar problemas de diseño de hardware más grandes. El trabajo se centra en tres áreas de aplicación, el procesamiento de imágenes, el procesamiento de paquetes de red y la inteligencia artificial, donde se analizan los requisitos del sistema y los retos de diseño, para posteriormente abordarlos, proponiendo soluciones.

En el área de procesamiento de imágenes, abordamos la compresión bajo estrictas restricciones, como las que se plantean en la exploración de satélites y drones. Dado que los algoritmos de compresión de imágenes disponibles no abordan adecuadamente los problemas en estos escenarios, se siguió un enfoque de codiseño algoritmo-hardware. Propusimos una serie de mejoras en el estándar JPEG-LS, destinadas a mejorar su eficiencia de codificación con una baja sobrecarga computacional, y luego, desarrollamos una implementación FPGA del codificador. Como resultado, se consiguió un compresor de baja latencia y con pérdidas matemáticamente acotas (near-lossless) con la mayor tasa de píxeles y la mayor relación de compresión, superando las implementaciones existentes.

En el área del procesamiento de paquetes de red, nos centramos en el problema de descargar el proceso de medición de flujos para 100 Gbit Ethernet. Aunque para velocidades de enlace más lentas una implementación de síntesis de alto nivel es capaz de proporcionar una solución, para el enlace objetivo y aplicaciones relevantes que requieren la gestión de grandes memorias, esta vía fue insuficiente. Por este motivo, se diseñó una arquitectura alternativa para abordar el problema de la implementación de procesos de lectura-actualización complejos y de alto rendimiento que se enfrentan a importantes retardos de propagación asociados al sistema de memoria. Esto permitió implementar en una FPGA un sistema de medición de flujos TCP capaz de soportar la tasa máxima de paquetes de 100 GbE y logrando una descarga de más del 50% de la carga computacional. También demostramos que el uso de arreglos de los módulos desarrollados permite utilizar tablas de flujos más grandes, lo que aumenta la capacidad de descarga, sin dejar de soportar la tasa máxima de paquetes.

Además, estudiamos una optimización de rendimiento complementaria para los procesos de lectura-actualización, la técnica de bloqueo condicional. Llegamos a la conclusión de que, con implementaciones eficientes, su utilización no tendrá penalizaciones de frecuencia para la mayoría de los diseños y que se requieren pocos recursos adicionales. Además, examinamos el rendimiento de la técnica en función de las características de los datos de entrada y de la arquitectura, mostrando que, incluso en casos adversos, puede mejorar significativamente el rendimiento. Sin embargo, demostramos que, para optimizar el rendimiento, hay que tener en cuenta tanto las estadísticas de direcciones de memoria, como la evolución de la frecuencia a medida que se incrementa la segmentación.

En el área de la inteligencia artificial, abordamos un conjunto de problemas de implementación relacionados que surgen al escalar aceleradores de redes neuronales convoluciones segmentados, en particular, en FPGAs no monolíticas (multi-SLR). Para abordarlos, desarrollamos una herramienta de optimización de particionamiento y balanceo de recursos. Esta herramienta determina la conexión de las señales de control de grandes diseños en FPGAs multi-SLR, y equilibra múltiples recursos a lo largo de las regiones y/o FPGAs, al tiempo que minimiza el coste de comunicación entre ellas. La herramienta mapea de forma nativa a una implementación multi-nodo si el diseño no cabe en una sola FPGA, y soporta diferentes paradigmas multi-nodo. Esta optimización mejoró significativamente el rendimiento de los aceleradores. La utilización de plataformas multi-nodo permitió mejorar la densidad de cálculo, la latencia y el consumo de energía.

Por último, a partir de la experiencia obtenida en el desarrollo de estas aplicaciones, identificamos aspectos metodológicos clave que nos condujeron a una exitosa implementación de hardware utilizando la síntesis de alto nivel (HLS, por sus siglas en inglés). En particular, observamos que HLS puede lograr muy buenos resultados, aprovechando una mayor exploración algorítmica y especialización de funciones. Además, identificamos las ventajas del particionamiento y refinamiento modular, y de la utilización de una mentalidad de desarrollo orientada al hardware.

#### **AGRADECIMIENTOS**

Esta tesis refleja el trabajo de poco más de cuatro años de mi vida. Claro es que si tuviese que nombrar a todas aquellas personas que lo influenciaron, el largo de la misma se duplicaría. Cuantas conversaciones afectaron mi forma de pensar, muchas con gente que nunca conocí. Dicho esto, hay personas que no puedo dejar de mencionar.

En primer lugar, quiero que agradecer a mi compañera en la vida, Luky, quien siempre estuvo al lado mío para luchar las más difíciles batallas. Sin ella, no veo como podría hoy estar cantando victoria. En estas batallas, nunca faltó mi familia. Mi mamá, Silvia, mi papá, Julio, y mi hermana, Tami. A quienes se sumaron mi nueva familia Melián. Aún a la distancia, a un centímetro de mí cuando los necesité.

En el campo, en Madrid, Alberto, Silvia, Rafa, Moni y Franco. Gracias por su amistad, sus consejos y los buenos momentos. En especial, menciono a Mario, gran amigo y compañero de laboratorio. Gracias por los consejos, discusiones, charlas y compañía en el laboratorio, en Madrid, en Argentina y en Dublín. Un miembro especial de mi equipo es Noela, a quien agradezco profundamente por prestarme su oído y ayudarme a crecer.

También, doy las gracias a Gustavo y a Jorge, mis directores, por todo lo que me enseñaron, por la oportunidad de trabajar con ellos y por la ayuda en el camino de llegar a ser doctor. Ya sea por charlas espontáneas o por el tiempo que me dedicaron, mis trabajos se beneficiaron de los miembros de HPCN. En particular, agradezco a Sergio, por su crítica constructiva y honesta. Durante estos años en el laboratorio, tuve grandes compañeros con quienes intercambié ideas, frustraciones, problemas, y soluciones. Por esto quiero agradecer a Angel, Dani, David, Edu, Guille, Jesus, Jose Fernando, Rafa y Sergio. Adicionalmente, agradezco a aquellos profesores de la Facultad de Ingeniería de la UNSJ que me dieron herramientas para enfrentar este desafío.

Last, but not least, I want to thank the Xilinx Research Labs team in Ireland for the great experience that I had working with them. In particular, thanks to Jakoba, Yaman, Guilio, Alina, Ela, Nick, and Michaela, for the help and jokes that made the job easy. Specially, I would like to thank Lucian, who guided me in my work. Thanks for all that he taught me, and for both the pragmatic and the idealistic discussions we had.

# LIST OF CONTENTS

|    |       |        |                                                              | Page  |

|----|-------|--------|--------------------------------------------------------------|-------|

| Li | st of | Tables | 5                                                            | xiii  |

| Li | st of | Figur  | es                                                           | xv    |

| Li | st of | Algori | thms                                                         | xviii |

| Ι  | Int   | rodu   | ction & Background                                           | 1     |

| 1  | Inti  | roduct | ion                                                          | 2     |

|    | 1.1   | Conte  | ext & Motivation of the Thesis                               | . 2   |

|    |       | 1.1.1  | Trends of Data Processing Requirements                       | . 2   |

|    |       | 1.1.2  | Trends of General Purpose Hardware Performance               | . 3   |

|    |       | 1.1.3  | Trends of Custom Designed Hardware and FPGAs                 | . 5   |

|    | 1.2   | Objec  | tives & Methodology of the Thesis                            | . 6   |

|    |       | 1.2.1  | Objectives                                                   | . 6   |

|    |       | 1.2.2  | Methodology                                                  | . 7   |

|    | 1.3   | Struct | ture of the Thesis                                           | . 9   |

| 2  | Inti  | roduce | ión                                                          | 10    |

|    | 2.1   | Conte  | exto y Motivación de la Tesis                                | . 10  |

|    |       | 2.1.1  | Tendencias de los Requerimientos de Procesamiento            | . 10  |

|    |       | 2.1.2  | Tendencias del Desempeño del Hardware de Propósito General . | . 11  |

|    |       | 2.1.3  | Tendencias del Hardware Diseñado a Medida y las FPGA         | . 13  |

|    | 2.2   | Objeti | ivos & Metodología de la Tesis                               | . 15  |

|    |       | 2.2.1  | Objetivos                                                    | . 15  |

|    |       | 2.2.2  | Metodología                                                  | . 16  |

|    | 2.3   | Estru  | ctura de la Tesis                                            | . 18  |

| 3  | Bac | kground                                                    | 19 |

|----|-----|------------------------------------------------------------|----|

|    | 3.1 | Electronic Circuit Technology                              | 19 |

|    | 3.2 | Design Languages                                           | 23 |

| II | Ca  | se Studies and Challenges Presentation                     | 25 |

| 4  | Ima | age Processing: Compression in Constrained Scenarios       | 26 |

|    | 4.1 | Introduction                                               | 26 |

|    | 4.2 | JPEG-LS                                                    | 28 |

|    |     | 4.2.1 JPEG-LS Baseline Algorithm                           | 28 |

|    |     | 4.2.2 JPEG-LS Extension                                    | 29 |

|    |     | 4.2.3 JPEG-LS Hardware Implementations                     | 29 |

|    | 4.3 | Asymmetric Numeral Systems                                 | 30 |

|    |     | 4.3.1 tANS Operation                                       | 31 |

|    |     | 4.3.2 Coding Efficiency                                    | 32 |

|    | 4.4 | Problem Analysis                                           | 32 |

|    |     | 4.4.1 Test Image Dataset                                   | 32 |

|    |     | 4.4.2 JPEG-LS Optimization Potential                       | 32 |

|    | 4.5 | Research & Development Goals                               | 36 |

| 5  | Con | nputer Networks: 100 GbE Flow Metering                     | 37 |

|    | 5.1 | Introduction                                               | 37 |

|    | 5.2 | Flow Monitoring                                            | 38 |

|    | 5.3 | State-of-the-Art                                           | 39 |

|    | 5.4 | Problem Analysis                                           | 41 |

|    |     | 5.4.1 Scenario                                             | 41 |

|    |     | 5.4.2 System Constraints                                   | 42 |

|    |     | 5.4.3 Required Hardware                                    | 44 |

|    | 5.5 | Research & Development Goals                               | 45 |

| 6  | AI: | Implementation of Large CNN Accelerators                   | 46 |

|    | 6.1 | Introduction                                               | 46 |

|    | 6.2 | Background                                                 | 48 |

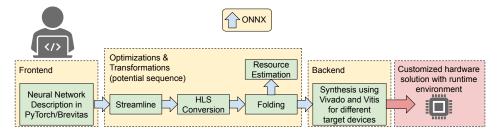

|    |     | 6.2.1 The FINN Compiler                                    | 48 |

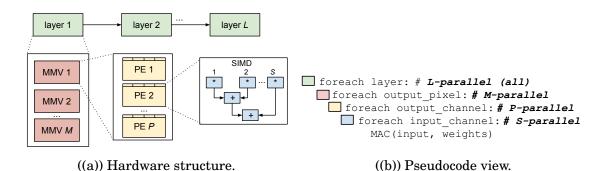

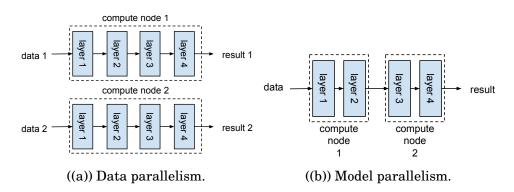

|    |     | 6.2.2 Scaling Up CCN Performance                           | 49 |

|    | 6.3 | Challenges in Scaling Up Dataflow Architecture Performance | 51 |

|    |      | 6.3.1  | Considerations for Large FPGA Designs               | 51 |

|----|------|--------|-----------------------------------------------------|----|

|    |      | 6.3.2  | Maximizing Compute Density                          | 52 |

|    | 6.4  | Resea  | rch & Development Goals                             | 54 |

|    |      |        |                                                     |    |

| II | I Ad | dress  | sing the Challenges                                 | 55 |

| 7  | LOO  | CO-AN  | S Image Codec: Algorithm                            | 56 |

|    | 7.1  | Introd | luction                                             | 57 |

|    | 7.2  | LOCO   | -ANS Overview                                       | 58 |

|    |      | 7.2.1  | High-Level Description                              | 58 |

|    |      | 7.2.2  | Encoding Algorithm Summary                          | 60 |

|    | 7.3  | An Al  | NS-based Coder for TSG Sources                      | 60 |

|    |      | 7.3.1  | Adaptive Bernoulli Coder                            | 61 |

|    |      | 7.3.2  | Basic Geometric Coder                               | 61 |

|    |      | 7.3.3  | Codification Order for ANS                          | 62 |

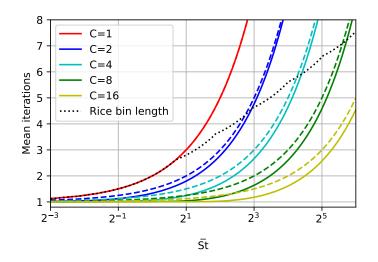

|    |      | 7.3.4  | Geometric Coder Iterations                          | 64 |

|    |      | 7.3.5  | Limitation of Coder Iterations and Symbol Expansion | 66 |

|    | 7.4  | Distri | bution Parameters Estimation                        | 69 |

|    |      | 7.4.1  | <i>p</i> Parameter Estimation                       | 69 |

|    |      | 7.4.2  | $\theta$ Parameter Estimation                       | 71 |

|    |      | 7.4.3  | Resets                                              | 73 |

|    | 7.5  | Select | ion of Coder Parameters                             | 74 |

|    |      | 7.5.1  | ANS Tables Limitations and Generation               | 74 |

|    |      | 7.5.2  | Selection Methodology                               | 76 |

|    |      | 7.5.3  | Tuning the Coder Parameters                         | 78 |

|    | 7.6  | Exper  | imental Results                                     | 79 |

|    |      | 7.6.1  | Analysis of LOCO-ANS Configurations Performance     | 81 |

|    |      | 7.6.2  | Experimental System Efficiency                      | 83 |

|    |      | 7.6.3  | Software Performance Comparison                     | 86 |

|    |      | 7.6.4  | Discussion                                          | 91 |

|    | 7.7  | Conclu | usion                                               | 92 |

| 8  | LOO  | CO-AN  | S Image Codec: Hardware Implementation              | 93 |

|    | 8.1  | Introd | luction                                             | 94 |

|    | 8.2  | Encod  | er Architecture                                     | 94 |

|    |      | 8.2.1    | Pixel Decorrelation                                                                                                         | 95  |

|----|------|----------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|    |      | 8.2.2    | TSG Coder                                                                                                                   | 100 |

|    | 8.3  | Result   | s                                                                                                                           | 104 |

|    |      | 8.3.1    | Test Platform and Encoder Configurations Description                                                                        | 104 |

|    |      | 8.3.2    | Implementation Results                                                                                                      | 106 |

|    |      | 8.3.3    | Results Evaluation                                                                                                          | 106 |

|    | 8.4  | Discus   | sion                                                                                                                        | 109 |

|    |      | 8.4.1    | Related work                                                                                                                | 109 |

|    |      | 8.4.2    | Comparison Considerations                                                                                                   | 112 |

|    |      | 8.4.3    | Lossless-only Encoders Comparison                                                                                           | 115 |

|    |      | 8.4.4    | Near-lossless Encoders Comparison                                                                                           | 116 |

|    | 8.5  | Conclu   | isions                                                                                                                      | 117 |

| 9  | 1000 | be Fl    | ow Metering & Dual Read-Update Architectures                                                                                | 119 |

|    | 9.1  | Introd   | uction                                                                                                                      | 120 |

|    | 9.2  | Archit   | cectures for the Flow Metering Core                                                                                         | 120 |

|    |      | 9.2.1    | Sequential Design                                                                                                           | 122 |

|    |      | 9.2.2    | Double-Frequency Multi-Cycle Architecture                                                                                   | 123 |

|    | 9.3  | Flow N   | Intering System Implementation                                                                                              | 126 |

|    |      | 9.3.1    | System Description                                                                                                          | 126 |

|    |      | 9.3.2    | Implementation                                                                                                              | 130 |

|    | 9.4  | Applic   | ation of the Architecture for Other Systems with the Read-Update                                                            |     |

|    |      | Patter   | n                                                                                                                           | 133 |

|    | 9.5  | Archite  | ecture Improvements                                                                                                         | 134 |

|    |      | 9.5.1    | Arrays of Flow Metering Cores                                                                                               | 134 |

|    |      | 9.5.2    | Double Frequency Architecture with Increased Pipelining                                                                     | 136 |

|    | 9.6  | Conclu   | sion                                                                                                                        | 137 |

| 10 | Stuc | ly of th | ne Conditional Stalling Technique                                                                                           | 139 |

|    | 10.1 | Introd   | uction                                                                                                                      | 139 |

|    | 10.2 | Impler   | nentation of Conditional Stalling                                                                                           | 142 |

|    | 10.3 | Modeli   | ng Conditional Stalling                                                                                                     | 143 |

|    |      | 10.3.1   | $\mathrm{II}_{\mathrm{sys}}$ Distribution for $DD = 1$                                                                      | 144 |

|    |      | 10.3.2   | Hidden Markov Model for $DD \ge 1$                                                                                          | 144 |

|    |      | 10.3.3   | A Simple $\overline{II}_{sys}$ Approximation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 146 |

|    | 10.4 | Perform  | mance Analysis                                                                                                              | 147 |

174

| 10.4.1 $II_{sys}$ Improvement for a given Processing Latency 14         | 7 |

|-------------------------------------------------------------------------|---|

| 10.4.2 Increasing Throughout Optimizing Pipeline Depth                  | 8 |

| 10.4.3 Trade-off Between $\mathrm{II}_{\mathrm{sys}}$ and Area $\ldots$ | 9 |

| 10.5 Application to 100 GbE Flow Metering                               | 0 |

| 10.6 Discussion                                                         | 1 |

| 10.7 Conclusion                                                         | 2 |

| 11 Automatic Partitioning and Resource Balancing 15                     | 3 |

| 11.1 Introduction                                                       | - |

| 11.2 Partitioning and Resource Balancing Tool                           |   |

| 11.2.1 Implementation Flow                                              |   |

| 11.2.2 Tool Capabilities                                                |   |

| 11.2.3 ILP Formulation                                                  |   |

| 11.2.4 Partitioner Implementation                                       |   |

| 11.2.5 FINN Integration                                                 |   |

| 11.3 Tool Evaluation                                                    | 1 |

| 11.3.1 Experimental and Implementation Setup                            | 1 |

| 11.3.2 Effect of Partitioning on Operating Frequency                    | 3 |

| 11.3.3 Effect on Compute Density                                        | 4 |

| 11.3.4 Effect of Scale-Out Alternatives on Latency and Power 16         | 6 |

| 11.4 Discussion                                                         | 8 |

| 11.4.1 Designer's Productivity                                          | 8 |

| 11.4.2 Tool Scalability 16                                              | 9 |

| 11.4.3 Design Methodology                                               | 0 |

| 11.5 Related work                                                       | 0 |

| 11.5.1 Multi-SLR FPGA Partitioning and Optimization                     | 0 |

| 11.5.2 Multi-node FPGA DNN Partitioning                                 | 1 |

| 11.6 Conclusion                                                         | 3 |

|                                                                         |   |

# **IV Putting All Together**

| 12 Lessons Learned Designing with HLS          | 175 |

|------------------------------------------------|-----|

| 12.1 Introduction                              | 175 |

| 12.2 Incorporating HLS for Better Productivity | 176 |

| 12.2.1 How HLS Improves Productivity           | 176 |

|    |       | 12.2.2 Software vs Hardware Development              | 179 |

|----|-------|------------------------------------------------------|-----|

|    |       | 12.2.3 Desired Methodology Characteristics           | 179 |

|    | 12.3  | Key Methodological Aspects                           | 180 |

|    |       | 12.3.1 Modular Design and Refinement                 | 180 |

|    |       | 12.3.2 Architecture Design                           | 183 |

|    |       | 12.3.3 Interface Design                              | 186 |

|    |       | 12.3.4 Analysis of Compilation Results               | 187 |

|    | 12.4  | Summary                                              | 188 |

|    | 12.5  | Conclusion                                           | 189 |

| 13 | Con   | clusions                                             | 190 |

|    | 13.1  | Main Contributions                                   | 190 |

|    | 13.2  | Future Work                                          | 194 |

| 14 | Con   | clusiones                                            | 196 |

|    | 14.1  | Principales Contribuciones                           | 196 |

|    | 14.2  | Trabajo Futuro                                       | 200 |

| A  | List  | of publications                                      | 202 |

|    | A.1   | Publications Included in the Contents of this Thesis | 202 |

|    |       | A.1.1 Journals & Magazines                           | 202 |

|    |       | A.1.2 International Conferences                      | 203 |

|    | A.2   | Other Publications Related to this Thesis            | 204 |

|    |       | A.2.1 International Conferences                      | 204 |

|    |       | A.2.2 Other Communications                           | 205 |

| B  | LOC   | CO-ANS compression examples                          | 206 |

| Bi | bliog | raphy                                                | 209 |

# **LIST OF TABLES**

| Т                                         | 'ABLE   Page                                                                                                    |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 3.1                                       | Example assembly program                                                                                        |

| $4.1 \\ 4.2$                              | Rawzor 8-bit gray dataset description33JPEG-LS bpp vs TSG models estimated entropy.35                           |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Neural networks accelerated in this work49Vivado resource utilization guidelines to avoid frequency penalties53 |

| $7.1 \\ 7.2$                              | Notation for LOCO-ANS description and analysis                                                                  |

| 7.3<br>7.5                                | Prototype configurations used in the experiments                                                                |

| 7.6<br>7.7                                | Number of images of the dataset that JPEG-LS achieves a lower bpp 83<br>Codec configurations used in the tests  |

| 7.8                                       | Encoder/Decoder speed comparison for lossless compression                                                       |

| 8.1 $8.2$                                 | Characteristics of target parts used in this work                                                               |

| 8.3                                       | LOCO-ANS Encoder implementation metrics                                                                         |

| 8.4<br>8.5                                | Comparison with other codec implementations                                                                     |

| 9.1<br>9.2                                | Notation used in the architectures analysis                                                                     |

|                                           | Stall stage HLS implementation performance comparison       142                                                 |

|                                           | $F_{\rm max}$ of baseline and partitioned single-node DNN accelerators                                          |

| 11.2                                      | Comparison of compute density achieved by the ILP tool against baseline 164                                     |

| 11.3 | Implemented ResNet-50 inference on two Alveo U280s at XACC   | 167 |

|------|--------------------------------------------------------------|-----|

| 12.1 | QoR impact due to alternative algorithm to reconstruct pixel | 177 |

# **LIST OF FIGURES**

| FIGURE |                                                                                                                                                                                 | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Processor performance evolution                                                                                                                                                 | . 3  |

| 1.2    | SPEC2017int speed results for Q1 2018-2022                                                                                                                                      | . 4  |

| 1.3    | Thesis methodology                                                                                                                                                              |      |

| 2.1    | Evolución del desempeño de los procesadores                                                                                                                                     | . 11 |

| 2.2    | Resultados de velocidad para SPEC2017<br>int para Q1 de 2018 a 2022                                                                                                             | . 13 |

| 2.3    | Metodología de la tesis                                                                                                                                                         | . 18 |

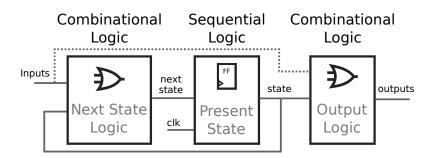

| 3.1    | Finite state machine structure                                                                                                                                                  | . 20 |

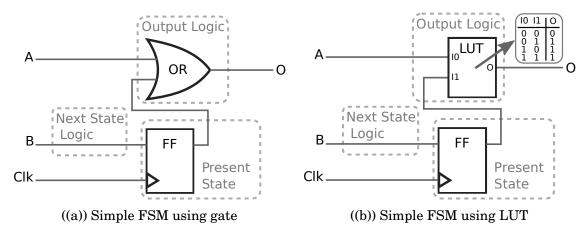

| 3.2    | Two equivalent implementations of a simple FSM                                                                                                                                  | . 20 |

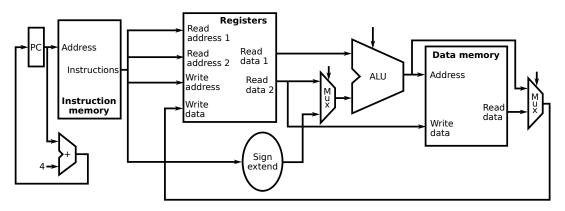

| 3.3    | Block diagram of a simple processor                                                                                                                                             | . 21 |

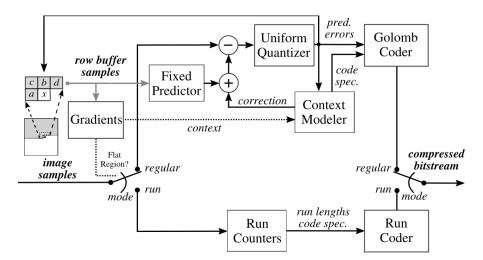

| 4.1    | High-level JPEG-LS encoder block diagram                                                                                                                                        | . 28 |

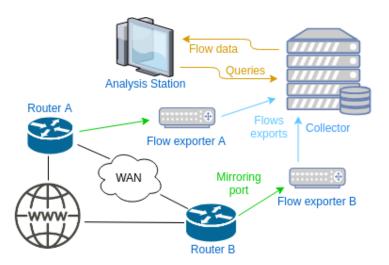

| 5.1    | Typical flow monitoring system                                                                                                                                                  | . 39 |

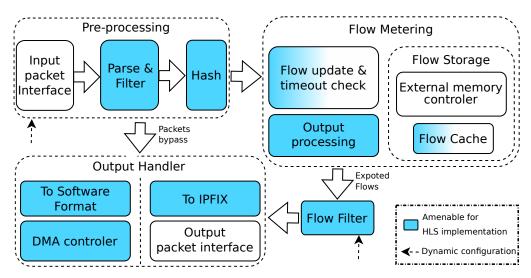

| 5.2    | Flow metering system high-level diagram                                                                                                                                         | . 41 |

| 5.3    | Performance of 100 GbE TCP flow metering with on-chip memory                                                                                                                    | . 44 |

| 6.1    | FINN Compiler Flow                                                                                                                                                              | . 48 |

| 6.2    | FINN parallelism dimensions for dense convolutions                                                                                                                              | . 50 |

| 6.3    | Data- and Model-Parallelism for multi-node implementations                                                                                                                      | . 50 |

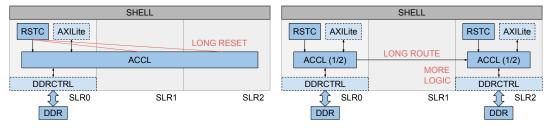

| 6.4    | Bad design decisions for large accelerators on multi-SLR FPGAs                                                                                                                  | . 52 |

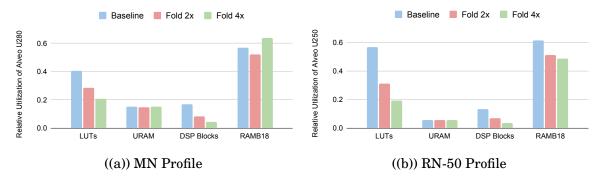

| 6.5    | Resource utilization as a function of folding                                                                                                                                   | . 53 |

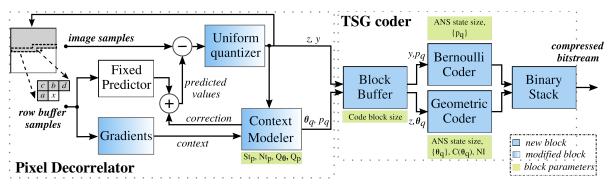

| 7.1    | LOCO-ANS block diagram                                                                                                                                                          |      |

| 7.2    | Geometric coder mean iterations as a function of $\overline{S_t}$                                                                                                               | . 65 |

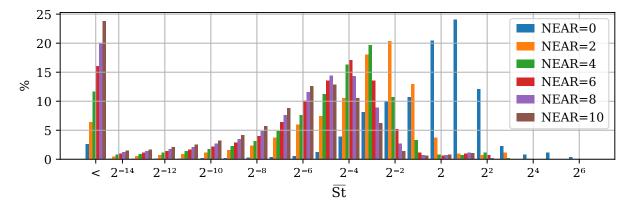

| 7.3    | $\overline{S_t}$ Histogram for Rawzor dataset for different NEAR $\ldots$                                                                                                       | . 65 |

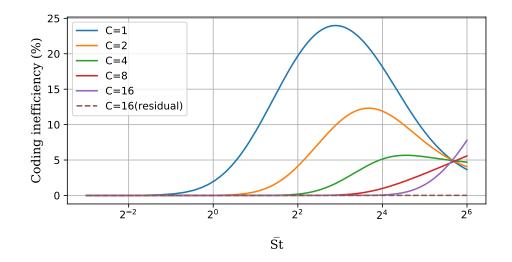

| 7.4    | Coding inefficiency caused by the iteration limitation mechanism using                                                                                                          | . 68 |

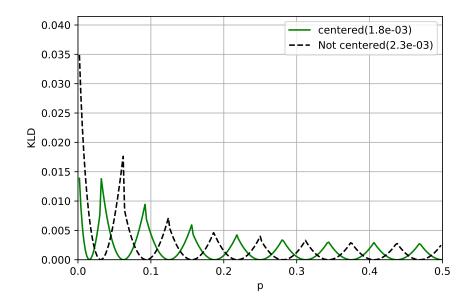

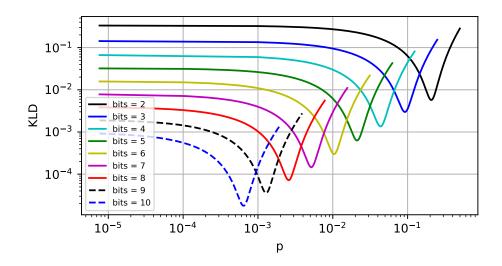

| 7.5    | KLD result of the $\hat{p}$ quantization $\ldots \ldots \ldots$ | . 71 |

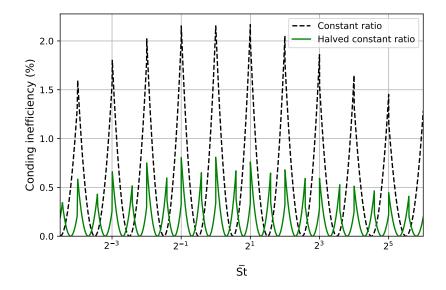

| 7.6  | Coding inefficiency due to the quantization of $\overline{S_t}$                           |

|------|-------------------------------------------------------------------------------------------|

| 7.7  | KLD of 2-symbol tANS tuned to the minimum symbol probability 75                           |

| 7.8  | Mean bpp using the prototype configurations with NI=7 and JPEG-LS $81$                    |

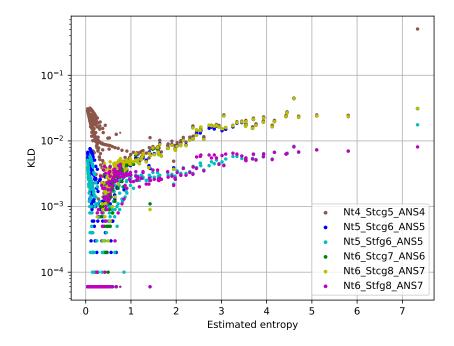

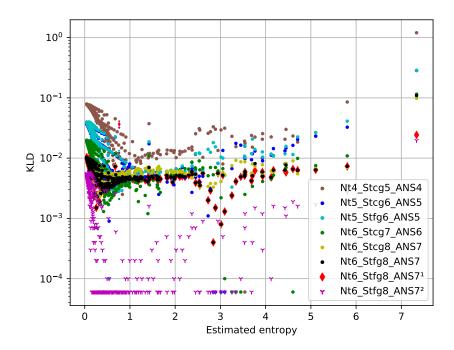

| 7.9  | KLD due to distribution parameter estimation inefficiencies                               |

| 7.10 | KLD due to coder inefficiencies                                                           |

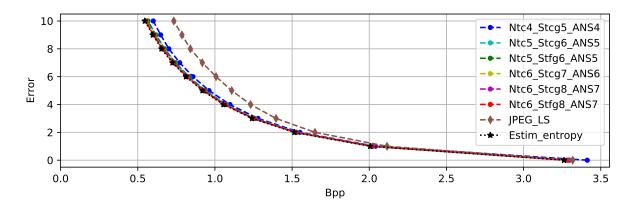

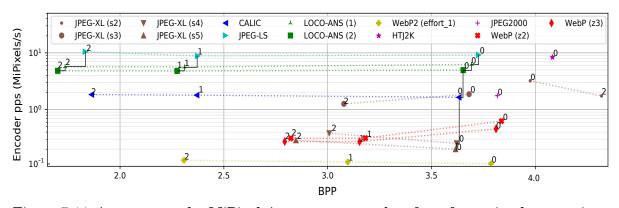

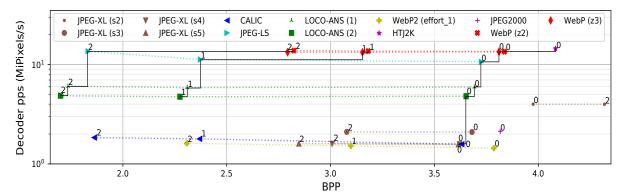

| 7.11 | Average encoder MiPixels/s versus average bpp for software comparison $\ldots$ 88         |

| 7.12 | Average decoder MiPixels/s versus average bpp for software comparison 89                  |

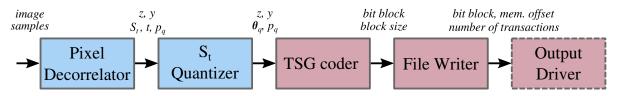

| 8.1  | LOCO-ANS hardware high-level block diagram                                                |

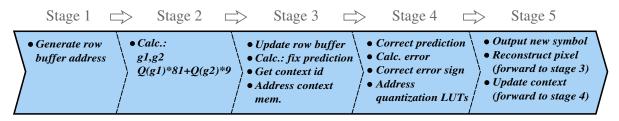

| 8.2  | Pixel decorrelator pipeline                                                               |

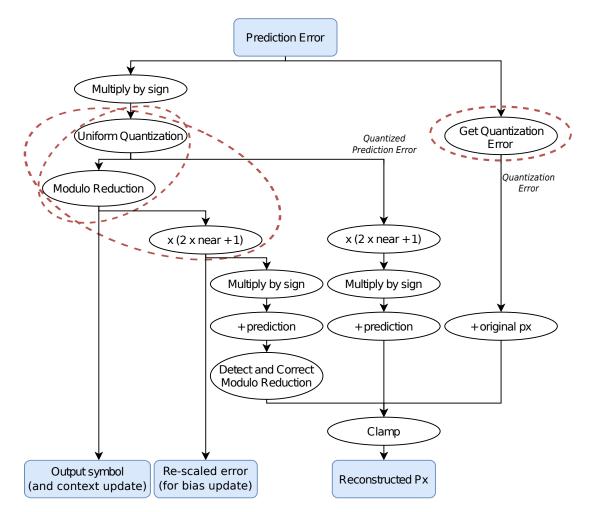

| 8.3  | LOCO-ANS quantization processes                                                           |

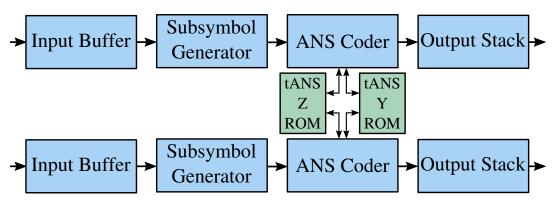

| 8.4  | High-level block diagram of the double lane TSG coder                                     |

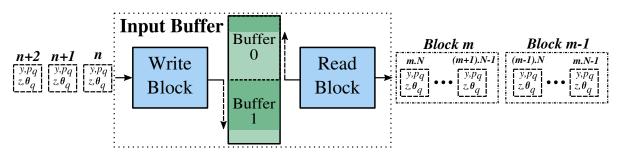

| 8.5  | Input Buffer block diagram, showing its operation for block size N. $\ldots$ . 101        |

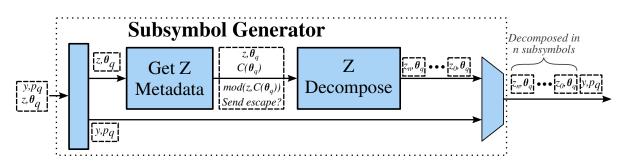

| 8.6  | Subsymbol Generator block diagram and data transformations within it $102$                |

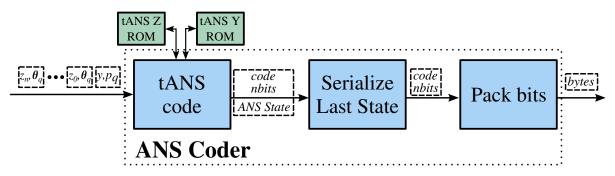

| 8.7  | tANS coder block diagram                                                                  |

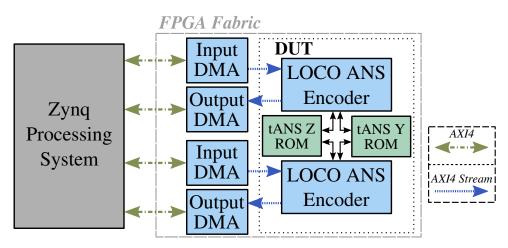

| 8.8  | Block diagram of the test system                                                          |

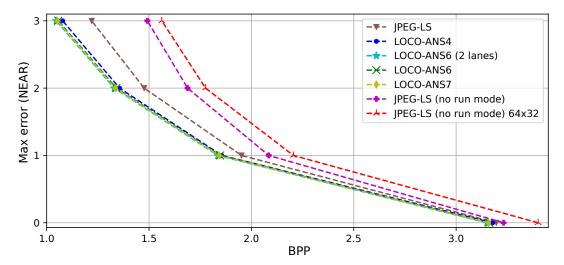

| 8.9  | D-R plane for JPEG-LS, JPEG-LS without run mode and LOCO-ANS 113                          |

| 9.1  | Sequential flow metering architecture                                                     |

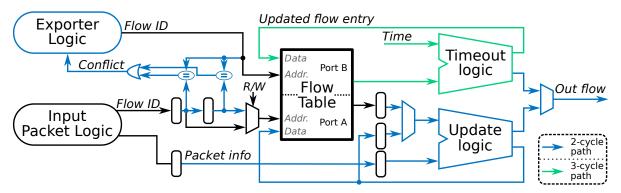

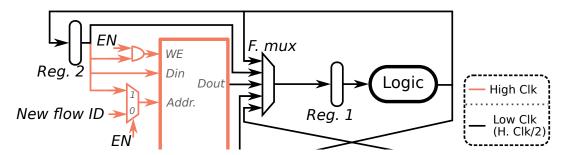

| 9.2  | Double-frequency multi-cycle architecture block diagram                                   |

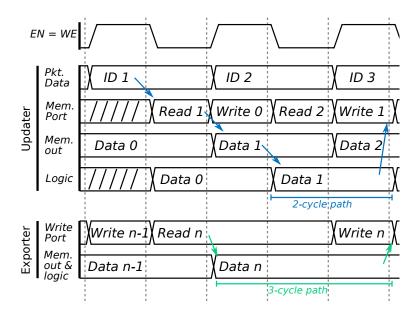

| 9.3  | Double-frequency multi-cycle architecture timing                                          |

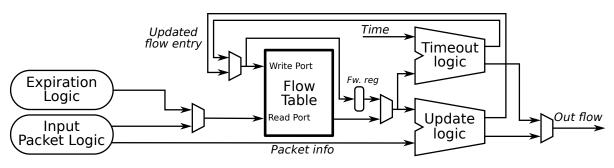

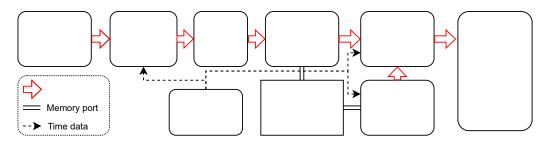

| 9.4  | High-level diagram of flow metering system                                                |

| 9.5  | SDNet parser code snippet                                                                 |

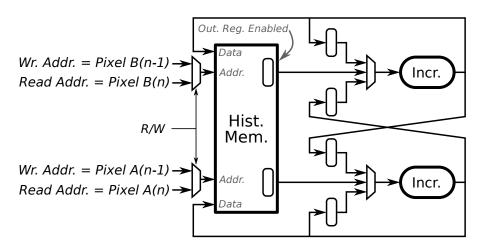

| 9.6  | Double-process histogram computation using the proposed architecture $\ \ldots \ 134$     |

| 9.7  | Implementation of four 64K flow probes in two SLRs running at $300 MHz$ 135               |

| 9.8  | Double frequency architecture with increased pipelining block diagram 137                 |

| 9.9  | Double frequency architecture with increased pipelining timing                            |

| 10.1 | Stalling stage HLS code                                                                   |

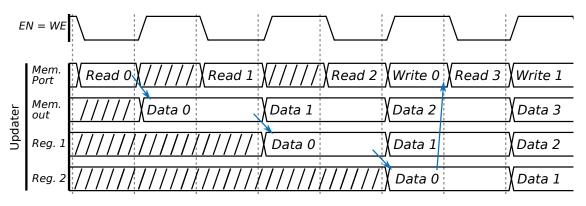

| 10.2 | Hidden Markov model example for $DD = 3$ and $C \ge 3$                                    |

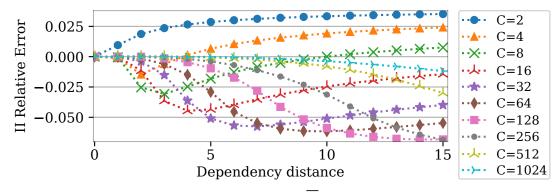

| 10.3 | Relative error of Eq. 10.2 with $\overline{II}_{lim}$ = 1.35 for random distributions 146 |

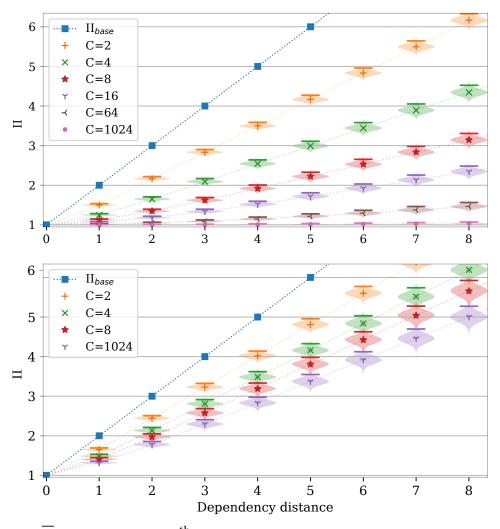

| 10.4 | Mean IIsys violin plots for blocks of 1000 packets for uniformly and Zipf $\ldots$ 147    |

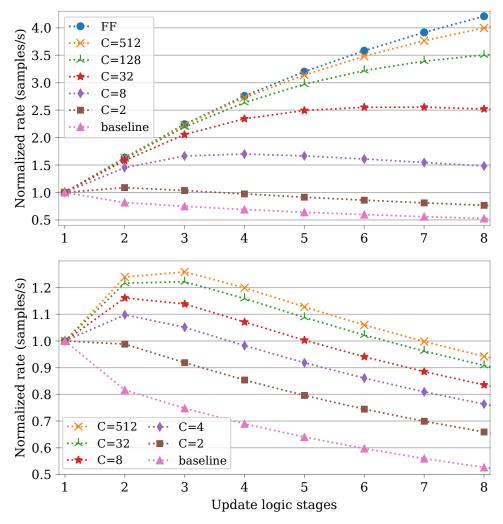

| 10.5 | Throughput estimation as a function of the processing module pipelining 148               |

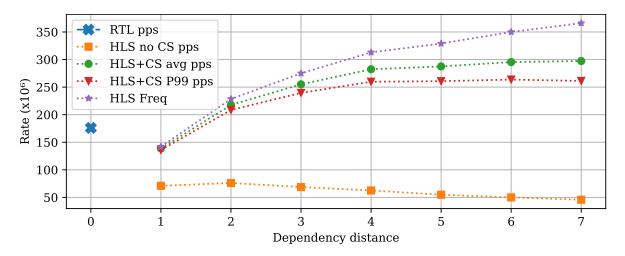

| 10.6 | Performance comparison of RTL and HLS design with and without CS $150$                    |

| 11.1 | Alternative system partitioning strategies                                                |

| 11.2 | Model parallelism alternatives                                                            |

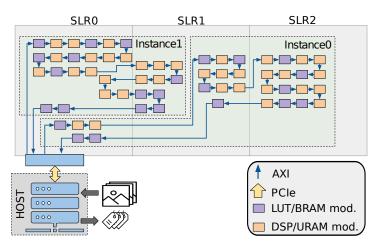

| Integration of the ILP partitioner into FINN                          |

|-----------------------------------------------------------------------|

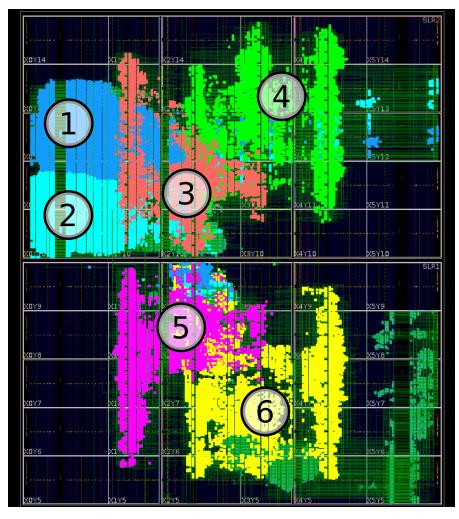

| Partition of 3xMN in 2xU280 (DP+TMP) 164                              |

| Partition of dual-version 2xMN in 1xU280                              |

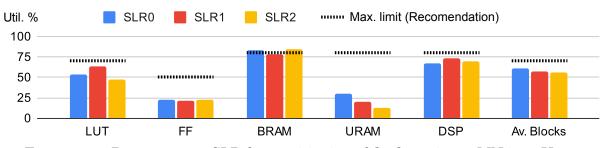

| Resources per SLR for partitioning of dual-version 2xMN in 1xU280 166 |

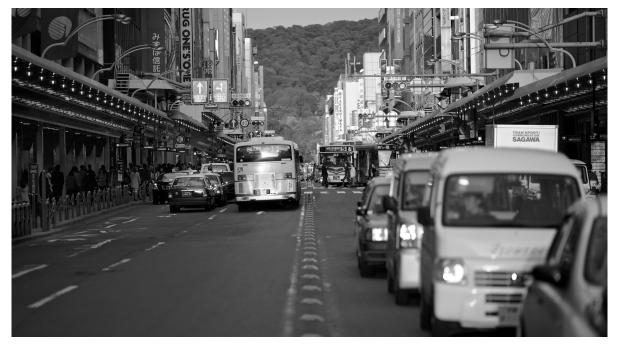

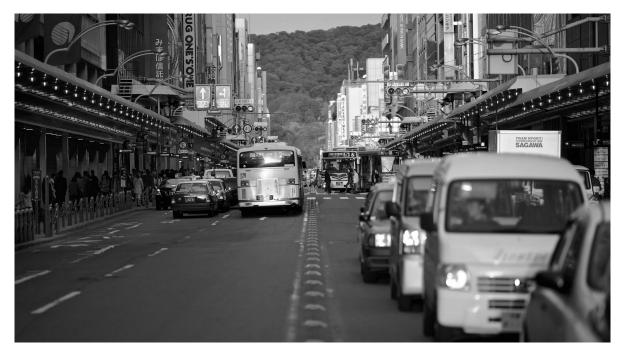

| Example picture 1 (reference)                                         |

| Example picture 1 (compressed with LOCO-ANS, NEAR=3)                  |

| Example picture 2 (reference)                                         |

| Example picture 2 (compressed with LOCO-ANS, NEAR=3)                  |

|                                                                       |

# LIST OF ALGORITHMS

#### ALGORITHM

#### Page

| 7.1  | Codification procedure of a geometrically distributed symbol using tANS. $% \left( {{{\bf{ANS}}}} \right)$ .          | 64  |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 7.2  | Codification of single $z$ limiting the iterations                                                                    | 67  |

| 7.3  | Estimation procedure of the $p$ Bernoulli parameter for a given context                                               | 70  |

| 7.4  | Halved constant ratio quantizer procedure for $\hat{	heta}_q$                                                         | 73  |

| 8.1  | Pixel loop algorithm structure                                                                                        | 96  |

| 8.2  | Coarse grained $	heta$ quantization function ( $Q_	heta$ ) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               | 97  |

| 8.3  | Error quantization and modulo reduction                                                                               | 98  |

| 12.1 | Codification procedure of a geometrically distributed symbol using tANS. $% \left( {{{\bf{x}}_{{\rm{s}}}}} \right)$ . | 181 |

| 12.2 | Algorithm 12.1 after loop splitting.                                                                                  | 182 |

| 12.3 | Efficient HLS implementation of Module 2 of algorithm 12.2                                                            | 184 |

# Part I

# **Introduction & Background**

#### **INTRODUCTION**

n this chapter, we detail the motivations and context of this thesis. This establishes the challenges we face and, therefore, the starting point upon which we set the objectives, and then, determine the methodology to achieve them. Finally, we

outline the structure of the rest of the thesis.

### **1.1 Context & Motivation of the Thesis**

#### 1.1.1 Trends of Data Processing Requirements

In many application areas, it is possible to see a continuous push towards higher performance systems in terms of bandwidth, latency, functionality, energy efficiency, among others. In the image and video processing area, the amount of data grows steadily as sensors and solutions target higher resolutions, number of colors, and frame rates. Other applications prioritize the improvement of different metrics, such as in the transmission of first-person view video for drone telecommand, where very low latencies have to be achieved. A generalization of this case are closed-loop control systems with video feedback, where increased latencies in the loop decrease the system's stability.

In computer networks, a similar trend is present. Connection bandwidth offered by Internet service providers has been growing at an exponential rate (approx. 50% per year) over the last decades, which is known as the Nielsen's law of Internet bandwidth [1]. Greater data rates bring many challenges, not only for the information delivery systems, but also for the mechanisms to analyze in real-time the health of this infrastructure.

Another example is found in the artificial intelligence area, where the great success of their algorithms, and, in particular, of artificial neural networks, in addressing problems that a few years ago were considered to be, in practice, out of reach for computers, impulsed a considerable number of applications that make use of this technology [2]. These range from high-throughput datacenter accelerated inference applications to critical embedded systems like advanced driver assistance systems (ADAS) and autonomous vehicles (AV). These applications, tend not only to consume big amounts of information, but also are very compute intensive.

#### 1.1.2 Trends of General Purpose Hardware Performance

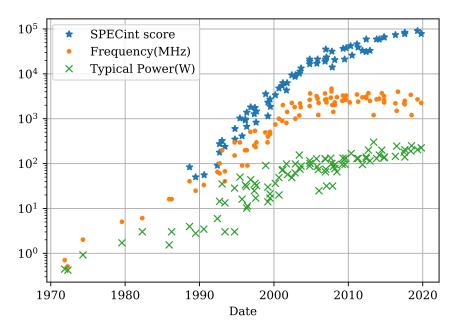

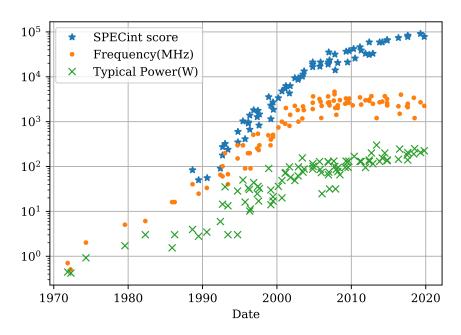

Contrasting with this increase in the data processing needs, the capacity of the leading technology (silicon semiconductors) to keep pushing performance forward is decreasing with each successive generation. Fig. 1.1 shows the performance evolution of general purpose processors over the last decades, measured by the SPECint benchmark and power. Until about 2004, new process nodes not only allowed doubling the transistor

Figure 1.1: Processor performance evolution. Data source: [3]

count per chip approx. every two years (Moore's Law [4]), but also increasing operation frequency while keeping power per unit area constant, which was accomplished using what is known as Dennard scaling [5]. This explains most of the performance increase shown in the figure until that year. After this, although higher transistor densities could be achieved, frequencies plateau and power started limiting performance.

For this reason, chip companies moved towards multicore architectures to keep increasing the work performed per unit of time. However, for a fix size problem, the speed-up experienced using parallelization faces diminishing returns, which is a function of the sequential portion of the procedures, as dictated by Amdahl's law [6]. Gustafson argued that as more compute power was available, the sizes of the problems we would try to tackle would increase, and with that, their parallel portion, resulting in an alternative formula for the speed-up accomplished by multicore systems, Gustafson's law [7]. Although this latter law is applicable to many problems, latency improvements are still governed by Amdahl's law, and power, chip area, among other constraints often limit the number of processing units that can be added. What is more, the increasing percentage of dark silicon (underutilized transistors) each new process node brings (caused by power dissipation issues derived from the end of Dennard scaling) does not allow multiplying the number of running cores (at peak performance) by the same factor the number of transistors grows [8]. In addition, other factors, like the memory system structure, also limits performance of general purpose hardware.

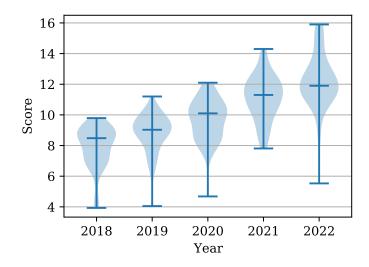

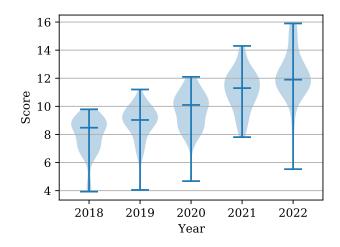

Figure 1.2: Violin plots showing SPEC2017int speed scores for the first quartile of each year. Minimum, median, and maximum values are marked. Data source: [9]

To observe in more detail what the trend has been over the last few years, we can analyze the published results of the SPEC2017int speed benchmark [9]. Fig. 1.2 shows the distribution of these results for the first quarter of each year. Although they correspond to high-end datacenter servers, the inter-annual performance rates, taking the maximum score as a reference, were 14.4%, 8.0%, 18.2%, and 11.2%, resulting in an average 12.9% increase per year (doubling performance every 5.7 years), which is a modest growth compared to what we have enjoyed in the previous decades. The median results have been growing slower at an average 8.2% inter-annual rate.

#### 1.1.3 Trends of Custom Designed Hardware and FPGAs

Considering these trends, at the present, it is increasingly necessary to resort to other means to improve performance. Leiserson *et al.* [10], foreseeing a potential stall in the miniaturization process for both physical and economic reasons, identified three areas that can push computer capacities forward: software performance engineering, algorithms, and hardware architecture. In particular, for the last two, they stress the importance of algorithm-hardware co-design and hardware specialization, which is inline with other works [11, 12].

Custom hardware has been a vital tool in many application areas, given that it can exceed the performance of other technologies, leveraging custom memory hierarchies, avoiding instruction fetch and decode logic, using custom operators, improving data reuse, among others. Also, nowadays, this alternative has become more profitable, given that general purpose hardware would take longer than in the past to reach the same level of performance. Yet, Application-Specific Circuit Technologies (ASICs) have high nonrecurring engineering cost (which are increasing), then these are normally only justified for high-volume production. Conversely, these costs are low for field programmable gate arrays (FPGA), thus enabling the use of custom-designed hardware in lower-volume applications. At the same time, FPGAs provide a greater flexibility, given the possibility of updating the implemented hardware, which, in turn, lowers development costs further as errors are easier to fix.

Nevertheless, FPGA have to compete against other specialized technologies like digital signal processors (DSP), graphic processing units (GPU) and application specific standard products (ASSP). Given their ease of use, flexibility and price, CPUs are, normally, the default target device. If system constraints cannot be met with them, for the same reasons, DSPs, GPUs and ASSPs tend to be the next devices to be considered. FPGAs are generally taken into account only if the previous options are not suitable for the task, as they are harder to program, so they have longer time-to-market and higher development costs. Because of this, the FPGA engineer normally confronts problems with stringent constraints in terms of latency, throughput, or power. Therefore, and considering that FPGAs achieve slower clock frequencies, efficient implementations are required, not only because of the hard nature of the problems they normally face, but also to fit the solution in smaller, cheaper chips to better compete in prices.

As a response to this situation, and to enable designers to develop larger systems, FPGA vendors, electronic design automation (EDA) companies and the academia are pushing towards easier FPGA programmability, and, in general, faster digital hardware design. For this, it is sought to move away from register transfer level (RTL) languages, like Verilog and VHDL, which require a more detailed specification and in-depth understanding of hardware and its design. As an alternative, researchers have worked in increasing the abstraction level, among other means, developing compilers to generate RTL from untimed languages, like C, C++ or Scala [13]. Although many of these tools have matured for more than a decade, their use still tends to imply a significant tradeoff between quality of results (QoR) and development time [14], which, as previously indicated, the FPGA designer cannot often afford.

### **1.2 Objectives & Methodology of the Thesis**

#### 1.2.1 Objectives

In this context, we consider fundamental to increase the hardware designer productivity, understood as the achieved performance per unit of developer time. In other words, our main objective is to reduce the time the designer needs to achieve a satisfactory system. To reach this objective, we take a holistic approach, targeting all the hardware design stages. That is, we aim to:

- Automate design tasks: Task automation is key to enable greater productivity, not only because the designer is freed from the task, at least partially, but also because computers are generally better at optimizing large high-dimensional spaces, so both development time and QoR can be improved simultaneously. Automating is particularly impactful when it is applied to error-prone processes, and also can enable less experienced designers to obtain expert-level QoR.

- **Obtain better architectures for common algorithm patterns:** For a given problem, architectures constitute different points in the design space, that is,

different trade-offs between latency, throughput, area, power, determinism, among others. For HLS to increase productivity in the sense stated above, it needs to be able to achieve not just a functionally correct system, but one that satisfies the often stringent constraints of FPGA applications. It is therefore important for HLS tools to have at their disposal a set of Pareto optimal architectures to implement different algorithm patterns.

- Obtain better algorithms for hardware implementation: Algorithms establish fundamental limitations to what can be achieved, and yet most algorithms were designed targeting the random-access machine [15]. As previously noted, algorithm-hardware co-design can be a key enabler of greater performance. For example, QuickSort [16] is a widely used and efficient sorting algorithm, but Bitonic sorting [17] may be preferred in GPU or FPGA implementations, despite being slower if run sequentially. This is because of its lower latency when run in parallel.

- Improve the hardware design methodology using high-level synthesis: misusing a good tool will lead us to poor results. Good methodologies allow us to get better results and in a reduced amount of time. It is therefore important to understand how to better use HLS and how to incorporate it in the hardware design process.

#### 1.2.2 Methodology

To achieve the objectives, we explore difficult problems in relevant areas, studying the systems requirements and identifying the design challenges. Although these may emerge from specific problems, we aim to provide solutions to a wider range of applications.

The selected areas and problems are the following:

- Network packet processing: In this area, we address the challenge of network flow metering offloading of 100 Gigabit Ethernet (GbE) links. Extensive work has been done to offload stateless network packet processing like filtering and routing, and these applications have even influenced how FPGA fabric is designed [18]. Yet, when it is necessary to keep a state, dependencies are established, which, added to the required high throughput that 100 GbE demands, constitutes a hard problem to face. Dependencies are common in many application areas, then strategies to ease them in one area, may be applied in others.

- **Image processing:** In this area, we address the problem of image lossless and near-lossless compression in highly constraint scenarios. Given the large amount

of data sensors are capable of producing, compression is often mandatory not only because of throughput limitations but also for power limitations, as data transmission is often the main contributor and harder to optimize process in terms of power [11]. On top of this, many applications also require low latency. Developments for this application may also be applied to other data compression algorithms, easing the power consumption problems faced from the embedded systems to datacenters.

• Artificial intelligence: In this area, we aim to implement large Convolutional Neural Networks (CNN) for datacenter application acceleration. This application is compute-intensive and highly parallelizable, thus suitable for FPGA acceleration. Although GPUs are also very suitable for CNN acceleration, CNN implemented as dataflows (all layers running concurrently in a large pipeline) in FPGAs allow larger accelerators to simultaneously increase throughput and decrease latency. Thus, these FPGA scaled up implementations may allow pushing the Pareto Frontier forward. However, the main challenge here is to face the problems that arise when these accelerators require spanning over the whole FPGA (specially for non-monolithic FPGAs) and even several FPGAs. Developments for this application may also be applied to other large-scale systems, which we will almost certainly face as data processing needs and the FPGA designer productivity continue to rise.

Notice that these applications cover a wide range of target devices, from small and generally cost and power optimized ones for image compression, passing through high-end medium/large FPGAs for 100 GbE flow metering, and finally, to large FPGA acceleration cards or clusters of them for CNN acceleration. For each of these problems, we first analyze the suitability of using higher level languages and tools to address them. If this leads to a successful development, we aim to identify those methodological components considered to be key contributors to the design success. When the higherlevel approach is deemed insufficient, we aim to understand why the tools do not address the problem efficiently, and to propose improvements to these tools or complementary ones. In some cases, we may observe opportunities to enhance available algorithms for their implementation in hardware, in those cases, we will also aim at improving them. Finally, through this process, solutions to the specific problems were be developed, which are also be considered contributions of this thesis.

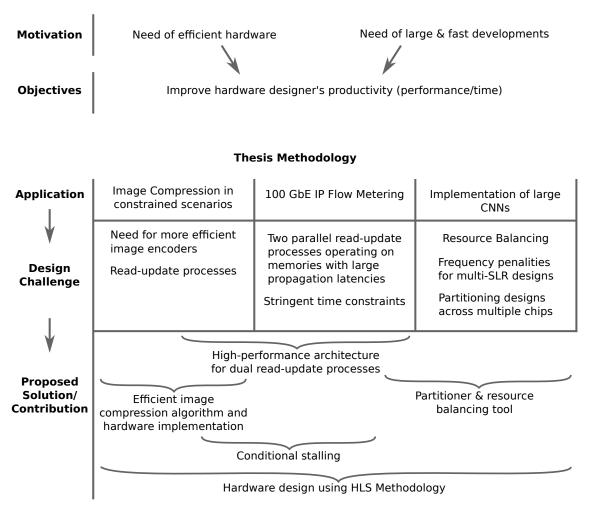

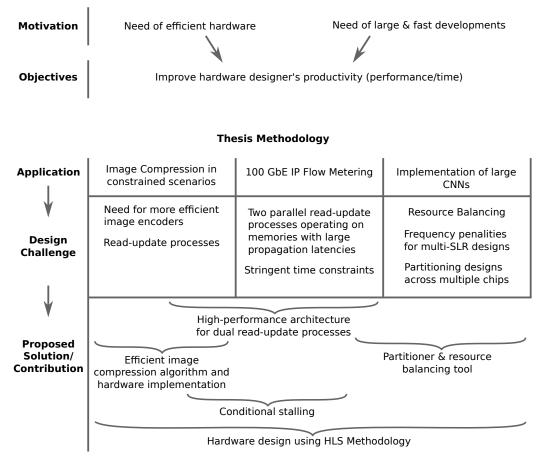

Fig. 1.3 serves as a summary, illustrating the relationship among the different components of this thesis.

Figure 1.3: Thesis methodology

#### **1.3 Structure of the Thesis**

This work is structured in four parts. The first one, *Introduction & Background*, includes this chapter and an additional one providing general background about FPGA design and high-level synthesis. Then, *Case Studies and Challenges Presentation* part is constituted by three chapters (one per application area), each of which introduces the application, providing specific background and analyses of the problems at hand, concluding with the determination of the specific research and development goals. After that, *Addressing the Challenges* part, includes a series of chapters, each of which provides solutions to the challenges identified in the previous part. Finally, the last *Putting All Together* part, presents key methodological aspects that led us to a successful hardware implementation using high-level synthesis and provides a summary of the contributions of this thesis. A brief abstract can be found at the beginning of each chapter.

#### **INTRODUCCIÓN**

n este capítulo detallamos las motivaciones y el contexto de esta tesis. En él se establecen los retos a los que nos enfrentamos y, por tanto, el punto de partida sobre el cual fijamos los objetivos y, a continuación, determinamos la metodología para alcanzarlos. Por último, esbozamos la estructura del resto

de la tesis.

#### 2.1 Contexto y Motivación de la Tesis

#### Tendencias de los Requerimientos de Procesamiento 2.1.1

En muchas áreas de aplicación, se observa un avance continuo hacia sistemas de mayor rendimiento en términos de ancho de banda, latencia, funcionalidad y eficiencia energética, entre otros. En el área de procesamiento de imágenes y vídeo, la cantidad de datos crece constantemente a medida que los sensores y las soluciones se orientan hacia mayores resoluciones, número de colores y velocidad de fotogramas. Otras aplicaciones priorizan la mejora de otras métricas, como en la transmisión de vídeo en primera persona para el telecontrol de drones, donde hay que conseguir latencias muy bajas. Una generalización de este caso son los sistemas de control de bucle cerrado con retroalimentación de vídeo, donde el aumento de las latencias en el bucle disminuye la

estabilidad del sistema.

En las redes de ordenadores se da una tendencia similar. El ancho de banda ofrecido por los proveedores de Internet ha crecido a un ritmo exponencial (aprox. 50% al año) durante las últimas décadas, lo que se conoce como la ley de Nielsen del ancho de banda de Internet [1]. Mayores tasas de datos conllevan muchos desafíos, no solo para los sistemas de entrega de información, sino también para los mecanismos de análisis en tiempo real de la salud de esta infraestructura.

Otro ejemplo lo encontramos en el área de la inteligencia artificial, donde el gran éxito de sus algoritmos y, en particular, de las redes neuronales artificiales, para abordar problemas que hace unos años se consideraban, en la práctica, fuera del alcance de los ordenadores, impulsó un número considerable de aplicaciones que hacen uso de esta tecnología [2]. Estas van desde aplicaciones de inferencia acelerada en centros de datos de alto rendimiento hasta sistemas integrados críticos como los sistemas avanzados de asistencia al conductor y los vehículos autónomos. Estas aplicaciones, además de consumir grandes cantidades de información, suelen ser muy intensivas en computación.

## 2.1.2 Tendencias del Desempeño del Hardware de Propósito General

Figure 2.1: Evolución del desempeño de los procesadores. Fuente de los datos: [3]

En contraste con este aumento de las necesidades de procesamiento de datos, la capacidad de la tecnología de punta (semiconductores de silicio) para seguir impulsando el rendimiento disminuye con cada generación sucesiva. La Fig. 2.1 muestra la evolución del rendimiento de los procesadores de propósito general en las últimas décadas, medido por el *benchmark* SPECint y la potencia consumida. Hasta aproximadamente 2004, los nuevos nodos de proceso no solo permitían duplicar el número de transistores por chip cada dos años aproximadamente (Ley de Moore [4]), sino también aumentar la frecuencia de funcionamiento manteniendo constante la disipación de energía por unidad de superficie, lo que se conseguía utilizando lo que se conoce como escalado de Dennard [5]. Esto explica la mayor parte del aumento de rendimiento mostrado en la figura hasta ese año. Después de esto, aunque se pudieron lograr mayores densidades de transistores, las frecuencias se estancaron y la disipación de energía comenzó a limitar el rendimiento.

Por esta razón, las empresas de chips se han movido hacia arquitecturas de múltiples núcleos para seguir aumentando el trabajo realizado por unidad de tiempo. Sin embargo, para un problema de tamaño fijo, el aumento de velocidad experimentado mediante la paralelización se enfrenta a rendimientos decrecientes, lo que es una función de la parte secuencial de los procedimientos, según dicta la ley de Amdahl [6]. Gustafson argumentó que, a medida que se dispusiera de más potencia de cálculo, aumentaría el tamaño de los problemas que intentáramos abordar y, con ello, su parte paralela, lo que dio lugar a una fórmula alternativa para el aumento de velocidad logrado por los sistemas multi-núcleo, la ley de Gustafson [7]. Aunque esta última ley es aplicable a muchos problemas, las mejoras de latencia siguen rigiéndose por la ley de Amdahl, y la potencia, el área del chip, entre otras restricciones, suelen limitar el número de unidades de procesamiento que pueden añadirse. Es más, el creciente porcentaje de silicio oscuro (transistores infrautilizados) que trae consigo cada nuevo nodo de proceso (provocado por los problemas de disipación de energía derivados del fin del escalado de Dennard) no permite multiplicar el número de núcleos en funcionamiento (a máximo rendimiento) por el mismo factor por el que crece el número de transistores [8]. Además, otros factores, como la estructura del sistema de memoria, también limitan el rendimiento del hardware de propósito general.

Para observar con más detalle cuál ha sido la tendencia en los últimos años, podemos analizar los resultados publicados del *benchmark* de velocidad SPEC2017int [9]. La Fig. 2.2 muestra la distribución de estos resultados para el primer trimestre de cada año. Aunque corresponden a servidores de centros de datos de gama alta, las tasas de rendimiento interanuales, tomando como referencia la puntuación máxima, han sido

Figure 2.2: Gráficos de violín que muestran las puntuaciones de velocidad de SPEC2017int para el primer cuartil de cada año. Se han marcado los valores mínimo, mediano y máximo. Fuente de los datos: [9]

del 14,4%, 8,0%, 18,2% y 11,2%, lo que supone un incremento medio del 12,9% por año (duplicando el rendimiento cada 5,7 años), lo que supone un crecimiento modesto comparado con el que hemos disfrutado en las décadas anteriores. La mediana de los resultados ha crecido más lentamente, a un ritmo medio del 8,2% interanual.

#### 2.1.3 Tendencias del Hardware Diseñado a Medida y las FPGA

Teniendo en cuenta estas tendencias, en la actualidad es cada vez más necesario recurrir a otros medios para aumentar el rendimiento. Leiserson *et al.* [10], previendo un posible estancamiento en el proceso de miniaturización por razones tanto físicas como económicas, identificaron tres áreas que pueden impulsar la capacidad de los ordenadores: ingeniería de desempeño de software, algoritmos y arquitecturas de hardware. En particular, para las dos últimas, destacan la importancia del co-diseño algoritmo-hardware y la especialización del hardware, lo que coincide con otros trabajos [11, 12].

El hardware a medida ha sido una herramienta vital en muchas áreas de aplicación, dado que puede superar el rendimiento de otras tecnologías, aprovechando jerarquías de memoria adaptadas, evitando la lógica de lectura y decodificación de instrucciones, utilizando operadores a medida, mejorando la reutilización de datos, entre otros. Además, hoy en día, esta alternativa es más rentable, dado que el hardware de propósito general tardaría más que en el pasado en alcanzar el mismo nivel de rendimiento. Sin embargo, las tecnologías de circuitos específicos para aplicaciones (ASIC, por sus siglas en inglés) tienen un alto coste de ingeniería no recurrente (que va en aumento), por lo que normalmente solo se justifican para la producción de grandes volúmenes. Por el contrario, estos costes son bajos en el caso de las matrices de puertas lógicas programables en campo (FPGA, por sus siglas en inglés), lo que permite el uso de hardware diseñado a medida en aplicaciones de menor volumen. Al mismo tiempo, las FPGA proporcionan una mayor flexibilidad, dada la posibilidad de actualizar el hardware implementado, lo que, a su vez, reduce aún más los costes de desarrollo, ya que los errores son más fáciles de corregir.

No obstante, las FPGA tienen que competir con otras tecnologías especializadas, como los procesadores de señales digitales (DSP, por sus siglas en inglés), las unidades de procesamiento gráfico (GPU, por sus siglas en inglés) y los productos estándar para aplicaciones específicas (ASSP, por sus siglas en inglés). Dada su facilidad de uso, flexibilidad y precio, las CPU son, normalmente, el dispositivo objetivo por defecto. Si las restricciones del sistema no pueden cumplirse con ellas, por las mismas razones, los DSP, las GPU y los ASSP suelen ser los siguientes dispositivos a tener en cuenta. Las FPGA suelen tenerse en cuenta solo si las opciones anteriores no son adecuadas para la tarea, ya que son más difíciles de programar, por lo que tienen un tiempo de comercialización más largo y unos costes de desarrollo más elevados. Por ello, el ingeniero de la FPGA suele enfrentarse a problemas con estrictas restricciones en términos de latencia, rendimiento o potencia. Por lo tanto, y teniendo en cuenta que las FPGAs alcanzan frecuencias de reloj más lentas, se requieren implementaciones eficientes, no solo por la dificultad de los problemas a los que normalmente se enfrentan, sino también para ser capaz de utilizar chips más pequeños y baratos para competir mejor en precios.

Como respuesta a esta situación, y para que los diseñadores puedan desarrollar sistemas más grandes, los proveedores de FPGA, las empresas de automatización del diseño electrónico (EDA, por sus siglas en inglés) y el mundo académico están impulsando una programabilidad más sencilla de las FPGA, y en general, del diseño de hardware digital. Para eso se busca alejarse de los lenguajes de nivel de transferencia de registros (RTL, por sus siglas en inglés), como Verilog y VHDL, que requieren una especificación más detallada y un conocimiento más profundo del hardware y su diseño. Como alternativa, los investigadores han trabajado en aumentar el nivel de abstracción, entre otros medios, desarrollando compiladores para generar RTL a partir de lenguajes no temporizados, como C, C++ o Scala [13]. Aunque muchas de estas herramientas han madurado desde hace más de una década, su uso todavía tiende a implicar un importante intercambio entre calidad de resultados (QoR, por sus siglas en inglés) y tiempo de desarrollo [14], que, como se ha indicado anteriormente, el diseñador de FPGAs a menudo no puede permitirse.

### 2.2 Objetivos & Metodología de la Tesis

#### 2.2.1 Objetivos

En este contexto, consideramos fundamental aumentar la productividad del diseñador de hardware, entendida como el rendimiento alcanzado por unidad de tiempo del desarrollador. En otras palabras, nuestro principal objetivo es reducir el tiempo que el diseñador necesita para conseguir un sistema satisfactorio. Para alcanzar este objetivo, adoptamos un enfoque holístico, dirigido a todas las etapas del diseño de hardware. Es decir, buscamos:

- Automatiza tareas de diseño: La automatización de tareas es clave para permitir una mayor productividad, no solo porque el diseñador se libera de la tarea, al menos parcialmente, sino también porque los ordenadores suelen ser mejores optimizadores de grandes espacios y de elevadas dimensiones, por lo que tanto el tiempo de desarrollo como la calidad de los resultados pueden mejorarse simultáneamente. La automatización es especialmente útil cuando se aplica a procesos propensos a errores, y también puede permitir a los diseñadores menos experimentados obtener resultados de calidad a nivel de experto.

- Obtener mejores arquitecturas para patrones de algoritmos comunes: Para un problema determinado, las arquitecturas constituyen diferentes puntos en el espacio de diseño, es decir, diferentes compromisos entre latencia, rendimiento, área, potencia, determinismo, entre otros. Para que HLS aumente la productividad en el sentido indicado, tiene que ser capaz de conseguir no solo un sistema funcionalmente correcto, sino uno que satisfaga las restricciones, a menudo estrictas, de las aplicaciones de las FPGA. Por lo tanto, es importante que las herramientas HLS tengan a su disposición un conjunto de arquitecturas pareto-óptimas para implementar diferentes patrones de algoritmos.

- **Obtener mejores algoritmos para la implementación en hardware:** Los algoritmos establecen limitaciones fundamentales a lo que se puede conseguir, y, sin embargo, la mayoría de los algoritmos se diseñaron pensando en la máquina de acceso aleatorio [15]. Como se ha señalado anteriormente, el co-diseño de algoritmos y hardware puede ser un factor clave para lograr un mayor rendimiento. Por

ejemplo, QuickSort [16] es un algoritmo de ordenación muy utilizado y eficiente, pero la ordenación bitónica [17] puede ser preferible en implementaciones de GPU o FPGA, a pesar de ser más lenta si se ejecuta secuencialmente. Esto es debido a su menor latencia cuando se ejecuta en paralelo.

• Mejorar la metodología de diseño de hardware utilizando la síntesis de alto nivel: un mal uso de una buena herramienta nos llevará a resultados pobres. Buenas metodologías nos permiten obtener mejores resultados y en un tiempo reducido. Por lo tanto, es importante entender cómo utilizar mejor HLS y cómo incorporarlo en el proceso de diseño de hardware.

#### 2.2.2 Metodología

Para lograr los objetivos, exploramos problemas difíciles en áreas relevantes, estudiando los requisitos de los sistemas e identificando los retos de diseño. Aunque estos surjan de problemas específicos, buscamos aportar soluciones a una gama más amplia de aplicaciones.

Las áreas y problemas seleccionados son los siguientes:

- Procesamiento de paquetes de red: En esta área, abordamos el reto de la descarga de la medición de flujos de red de los enlaces de 100 Gigabit Ethernet (GbE). Se ha realizado un amplio trabajo para descargar el procesamiento de paquetes de red sin estado, como el filtrado y el enrutamiento, y estas aplicaciones han influido incluso en la forma en que se diseña el tejido FPGA [18]. Sin embargo, cuando es necesario mantener un estado, se establecen dependencias que, sumadas al alto rendimiento requerido que exige 100 GbE, constituyen un problema difícil de afrontar. Las dependencias son comunes en muchas áreas de aplicación, luego las estrategias para aliviarlas en un área, pueden aplicarse en otras.

- **Procesamiento de imágenes:** En esta área, abordamos el problema de la compresión de imágenes sin pérdidas y casi sin pérdidas en escenarios con estrictas restricciones. Dada la gran cantidad de datos que los sensores son capaces de producir, la compresión es a menudo obligatoria no solo por las limitaciones de ancho de banda, sino también por las de potencia, ya que la transmisión de datos es a menudo el principal contribuyente y el proceso más difícil de optimizar en términos de consumo de potencia [11]. Además, muchas aplicaciones también requieren una baja latencia. Los desarrollos para esta aplicación también pueden aplicarse a otros

algoritmos de compresión de datos, aliviando los problemas de consumo de energía a los que se enfrentan desde los sistemas embebidos hasta los centros de datos.

• Inteligencia artificial: En esta área, nuestro objetivo es implementar grandes redes neuronales convolucionales (CNN, por sus siglas en inglés). Esta aplicación requiere una gran cantidad de cálculos y es altamente paralelizable, por lo que es adecuada para la aceleración mediante FPGA. Aunque las GPU también son muy adecuadas para la aceleración de CNN, las CNN implementadas como flujos de datos (todas las capas se ejecutan simultáneamente usando circuitos segmentados con una gran cantidad de etapas) en FPGA permiten que los aceleradores más grandes aumenten el rendimiento y reduzcan la latencia simultáneamente. Por lo tanto, estas implementaciones escaladas en FPGAs pueden permitir que se empuje la frontera de Pareto. Sin embargo, el principal reto aquí es hacer frente a los problemas que surgen cuando estos aceleradores requieren abarcar toda la FPGA (especialmente en el caso de las FPGAs no monolíticas) e incluso utilizar varias FPGAs. Los desarrollos para esta aplicación también pueden aplicarse a otros sistemas a gran escala, a los que nos enfrentaremos casi con toda seguridad a medida que las necesidades de procesamiento de datos y la productividad de los diseñadores de FPGA sigan aumentando.

Nótese que estas aplicaciones cubren una amplia gama de dispositivos objetivo, desde los pequeños y generalmente optimizados en coste y potencia para la compresión de imágenes, pasando por FPGAs de gama media/grande para la medición de flujo de 100 GbE, y finalmente, hasta grandes tarjetas de aceleración FPGA o conjunto de ellas para la aceleración de CNN. Para cada uno de estos problemas, analizamos primero la idoneidad de utilizar lenguajes y herramientas de alto nivel para abordarlos. Si esto conduce a un desarrollo exitoso, pretendemos identificar aquellos componentes metodológicos que se consideran clave para el éxito del diseño. Cuando el enfoque de mayor nivel de abstracción se considera insuficiente, pretendemos entender por qué las herramientas no abordan el problema de forma eficiente, y proponer mejoras a las mismas u otras complementarias. En algunos casos, podemos observar oportunidades para mejorar los algoritmos disponibles para su implementación en hardware, en esos casos, también nos propondremos mejorarlos. Finalmente, a través de este proceso, se desarrollarán soluciones a los problemas concretos, que también se considerarán contribuciones de esta tesis.

La Fig. 2.3 sirve de resumen, ilustrando la relación entre los diferentes componentes de esta tesis.

Figure 2.3: Metodología de la tesis

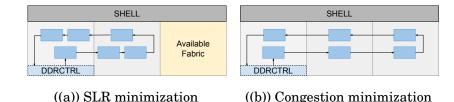

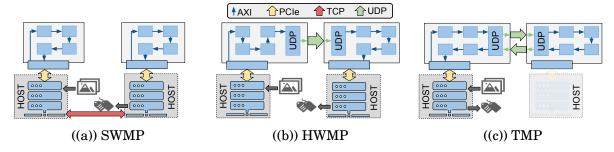

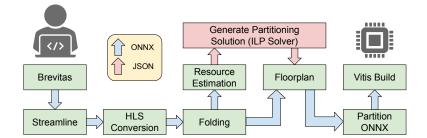

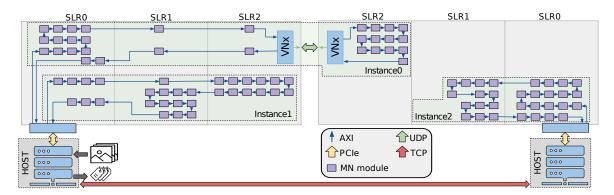

#### 2.3 Estructura de la Tesis